### Generische und betriebssystemgewahre statische Analysen von Echtzeitapplikationen auf Ein- und Mehrkernsystemen zur Optimierung nichtfunktionaler Eigenschaften

Der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades

DOKTOR-INGENIEUR

(abgekürzt: Dr.-Ing.)

vorgelegte Dissertation

von Herrn

Gerion Entrup, M. Sc.

geboren am 23. Mai 1991

in Osterncappeln, Deutschland

1. Referent **Prof. Dr.-Ing. habil. Daniel Lohmann**

2. Referent Prof. Dr.-Ing. Peter Ulbrich

Tag der Promotion ausstehend

### Kurzfassung

Eingebettete Systeme sind in ein sie umgebendes System integrierte Rechensysteme. Im Gegensatz zu generischen Rechensystemen erfüllen sie damit nur eine, vor ihrer Inbetriebnahme bereits festgelegte Funktion. Oft sind an diese Funktion auch noch zeitlich kritische Bedingungen geknüpft, die das System zu einem Echtzeitsystem machen. Beides eröffnet ein Potential für statische Maßschneiderung, das das der generischen Systeme übersteigt. Statische Maßschneiderung benötigt immer eine vorhergehende statische Analyse, die der anschließenden Optimierung die notwendigen Informationen zuführt. In dieser Arbeit bewege ich mich in diesem Feld und entwerfe dazu verschiedene betriebsgewahre statische Analysen, die eine Echtzeitanwendung um die Verwendung des Echtzeitbetriebssystems analysieren. Sie haben dabei das primäre Ziel der anschließenden Maßschneiderung und Optimierung des Echtzeitbetriebssystems auf die Anwendung und die damit einhergehende Verbesserung der nichtfunktionalen Eigenschaften des Gesamtsystems.

Neben der Grundlagenvorstellung bettet der erste Teil der Arbeit dazu erstmals die verwandten Vorarbeiten in einen theoretischen Kontext, der deren Schwächen aufzeigt: Sie sind in verschiedener Kombination nur auf statische Systeme anwendbar, arbeiten nur mit genau einer Echtzeitbetriebssystemschnittstelle, können nur mit Systemen mit einem Kern umgehen oder liefern keine Informationen bezüglich möglicher Optimierung.

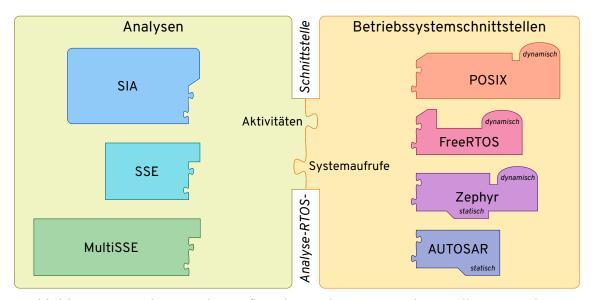

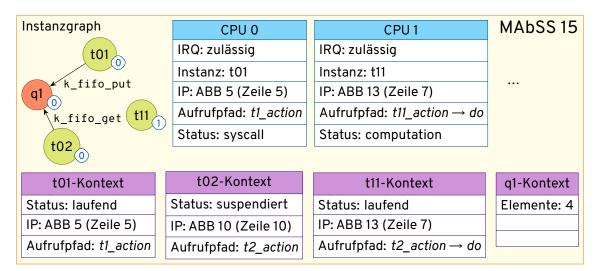

Mit ARA habe ich ein statisches Analyse-Framework geschaffen, das diese Probleme angeht: Es kombiniert verschiedene bestehende und neuentwickelte statische Analysen mit verschiedenen Echtzeitbetriebssystemmodellen und ist so in der Lage, eine Vielzahl von Echtzeitanwendungen automatisiert zu analysieren und passende Informationen für eine nachgelagerte Optimierung zu liefern. Konkret beinhaltet ARA die neu geschaffene statische Instanz- und Interaktionsanalyse, die Anwendungen untersuchen können, die gegen eine dynamische Echtzeitsystemschnittstelle geschrieben wurden. Sie ermitteln dort die Menge der dynamisch erstellten Betriebssystemobjekte und deren Interaktionen. Überdies ermöglicht die neu entwickelte MultiSSE eine vollständige abstrakte Analyse eines Mehrkernsystems. Sie bildet den dabei notwendigen abstrakten Betriebssystemzustand über alle Kerne nur an den Stellen, an denen dieser durch Kontrollflussinformationen oder eine Zeitanalyse notwendig ist. Durch die Trennung der Analysen in betriebssystemspezifische und generische Teile, sowie dem Entwurf einer gemeinsamen Schnittstelle zwischen verschiedenen Echtzeitbetriebssystemen konnte ich anschließend die Analysen betriebssystemagnostisch mit Anwendungen für AUTOSAR OS, FreeRTOS, Zephyr und POSIX durchführen und evaluieren.

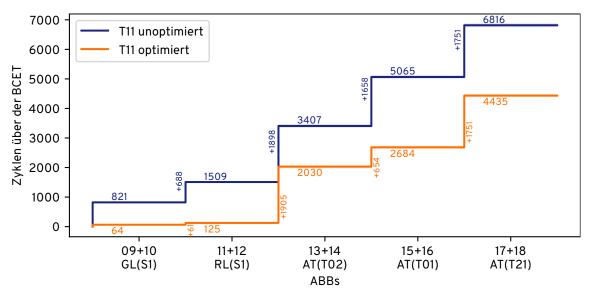

Meine Forschungsgruppe hat verschiedene Synthesen entwickelt, die auf Basis der Analyseergebnisse ein optimiertes System erzeugt haben. Wir konnten dabei die Systemstartzeit bei dynamischen Systemen um bis zu 44% senken und eine Verbesserung des Schlupfes um bis zu 35% für Mehrkernsysteme erreichen. Ich konnte überdies die Wirksamkeit der Schnittstelle mit der Analyse von 8 Echtweltanwendungen zeigen. In der Domäne der eingebetteten Systeme zeigt diese Arbeit als Ergebnis somit die erfolgreiche Erweiterung von betriebssystemgewahren Analysen auf dynamische Systeme und Mehrkernsysteme sowie deren Generalisierung in einem gemeinsamen Framework, das den Vergleich und das Ausführen verschiedener Analysen mit Anwendungen verschiedener Echtzeitbetriebssysteme ermöglicht.

*Schlüsselwörter* — betriebssystemgewahre Analyse, Mehrkernanalyse, Echtzeitsysteme, dynamische Systeme

### **Abstract**

Embedded systems are computing systems integrated into a surrounding system. In contrast to generic computing systems, they only fulfill a function that is strictly predefined before runtime. Often, it additionally contains time-critical constraints that make the system a real-time system. Both properties give a potential for static optimization that exceeds that of generic systems. Static tailoring always requires a prior static analysis that provides the necessary information for the subsequent optimization. In this work, I develop multiple such static analyses. They all analyze how an application uses the real-time operating system for a following tailoring of the operating system to the application resulting in an improvement of the non-functional properties of the overall system.

Besides foundational work, the first part of this thesis embeds the related existing analyses in a theoretical context for the first time, showing their weaknesses: In various combinations, these analyses only work with static systems, are only able to understand exactly one real-time—operating-system interface, can only deal with systems with one core or do not provide any information regarding possible optimization.

With ARA, I have created a static analysis framework that addresses these problems: It combines various existing and newly developed static analyses with different real-time–operating-system models and is thus able to automatically analyze a variety of applications providing information for a following optimization. Specifically, ARA includes the newly created static instance and interaction analysis, two analyses that can analyze applications that are written against a dynamic real-time–operating-system interface. They determine the number of dynamically created operating-system objects and their interactions. With the MultiSSE, I have also developed an analysis that allows a complete abstract analysis of a multi-core system. It creates the necessary abstract operating-system state across all cores only at those points where it is necessary due to control flow information or a time analysis. By separating the analyses into an operating-system–specific and a generic part, as well as the design of a common interface between different real-time operating systems, I was additionally able to apply the analyses in an operating-system–agnostic way with applications for AUTOSAR OS, FreeRTOS, Zephyr and POSIX.

My research group has developed various syntheses for creating an optimized system based on the analyses results. We were able to lower the system-start time for dynamic system up to 44% and an get an improvement of slack of up to 35% for multi-core systems. Furthermore, I was also able to demonstrate the effectiveness of the interface by analyzing 8 real-world applications. In the embedded-systems domain, this thesis thus demonstrates the successful extension of operating-system—aware analyses to dynamic systems and multi-core systems as well as their generalization in a common framework that enables the comparison and execution of different analyses with applications of different real-time operating systems.

*keywords* — operating-system aware analysis, multi-core analysis, real-time systems, dynamic systems

# Inhalt

| 1      | Einleitung                                      |

|--------|-------------------------------------------------|

| 1.1    | Motivation                                      |

| 1.2    | Forschungskontext 4                             |

| 1.3    | Zweck dieser Arbeit 6                           |

| 1.4    | Aufbau der Arbeit 9                             |

| 1.5    | Typographische Konventionen                     |

|        |                                                 |

| Teil I | Grundlagen 11                                   |

| 2      | Eingebettete und Echtzeitsysteme                |

| 2.1    | Eingebettete Systeme                            |

| 2.1.1  | Maßgeschneiderte Systeme durch Optimierung      |

| 2.1.2  | Lebensphasen                                    |

| 2.2    | Echtzeitsysteme                                 |

| 2.2.1  | Jobs und Tasks                                  |

| 2.2.2  | Fristen ("Deadlines")                           |

| 2.2.3  | Ablaufplanung ("Scheduling")                    |

| 2.3    | Echtzeitbetriebssysteme                         |

| 2.3.1  | AUTOSAR                                         |

| 2.3.2  | POSIX                                           |

| 2.3.3  | FreeRTOS         26           Zephyr         27 |

| 2.3.5  | Die Systemaufruf-Schnittstelle                  |

| 2.4    | Vom Modell zur Anwendung                        |

| 2.5    | Die Analyse von eingebetteten Systemen          |

| 2.6    | Zusammenfassung                                 |

| 0      |                                                 |

| 3      | Statische Analyse                               |

| 3.1    | Korrektheit und Vollständigkeit                 |

| 3.2    | Die Methode der Abstrakten Interpretation       |

| 3.3    | Terminierung der Analyse                        |

| 3.4    | Kontrollflussgraph und Gleichungssystem         |

| 3.5    | Widening                                        |

| 3.6    | Mehrkernanalyse                                 |

| 3.7    | Wertanalyse                                     |

| 3.8    | Zusammenfassung                                 |

| 4      | Betriebssystemgewahre Analyse 49                |

| 4.1    | Allgemeines Forschungsfeld                      |

| 4.2    | Astrée 51                                       |

| 4.3    | GORLINT 53                                      |

| 4.4     | RTSC                                            | 53  |

|---------|-------------------------------------------------|-----|

| 4.5     | dosek                                           | 55  |

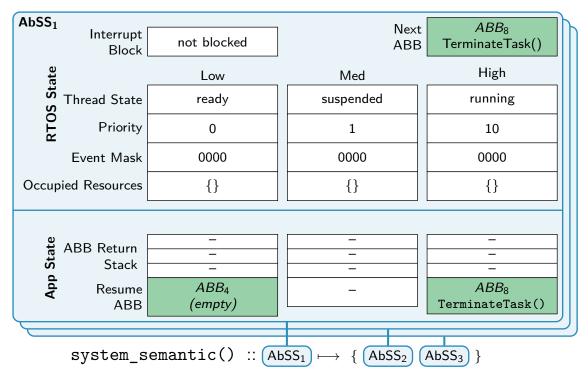

| 4.5.1   | Die System-State Enumeration (SSE)              | 58  |

| 4.5.2   | Der System-State Flow (SSF)                     | 60  |

| 4.6     | Diskussion                                      | 61  |

| 4.6.1   | Theoretische Einordnung der SSE und SSF         | 61  |

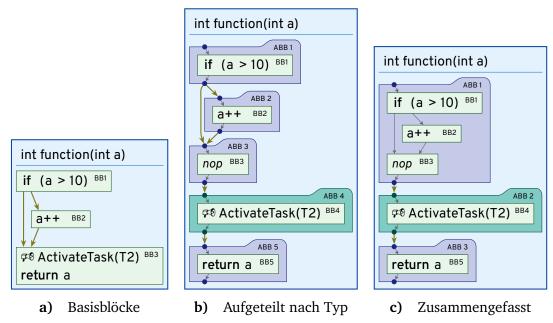

| 4.6.2   | Atomare Basisblöcke                             | 64  |

| 4.6.3   | Analyse-Restriktionen                           | 65  |

| 5       | ARA                                             | 67  |

| 5.1     | Überblick                                       | 68  |

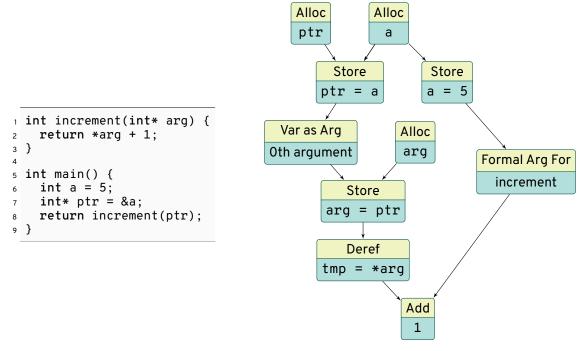

| 5.2     | Interprozeduraler Kontrollfluss                 | 69  |

| 5.3     | Wertanalyse                                     |     |

| 5.4     | Atomare Basisblöcke                             |     |

|         | Zusammenfassung                                 |     |

| 5.5     | Zusammemassung                                  | /4  |

| ·1      |                                                 |     |

| Teil II | I Konzepte                                      | 75  |

| 6       | Statische Analyse dynamischer Systeme           | 77  |

| 6.1     | Der Instanzgraph                                | 82  |

| 6.2     | Die Statische Instanzanalyse (SIA)              | 83  |

| 6.2.1   | Klassifizierung von Systemaufrufen              | 85  |

| 6.2.2   | Traversierung des Kontrollflussgraph            | 86  |

| 6.2.3   | Metadaten: Schleifen, Verzweigungen & Rekursion | 92  |

| 6.3     | Synthese                                        | 94  |

| 6.3.1   | Instanzsynthese                                 | 94  |

| 6.3.2   | Interaktionssynthese                            | 96  |

| 6.4     | Evaluation                                      | 98  |

| 6.4.1   | Messaufbau                                      | 98  |

| 6.4.2   | Microbenchmarks                                 |     |

| 6.4.3   | LibrePilot                                      |     |

| 6.4.4   | GPSLogger                                       |     |

| 6.5     | Diskussion                                      | 106 |

| 7       | Die Analyse von Mehrkernsystemen                | 109 |

| 7.1     | Voraussetzungen                                 | 111 |

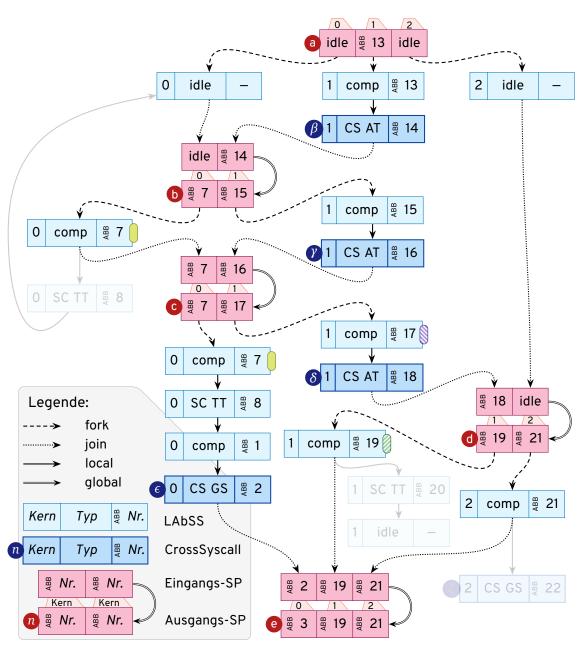

| 7.2     | Demonstration am laufenden Beispiel             | 111 |

| 7.3     | Funktionsweise der MultiSSE (Überblick)         | 113 |

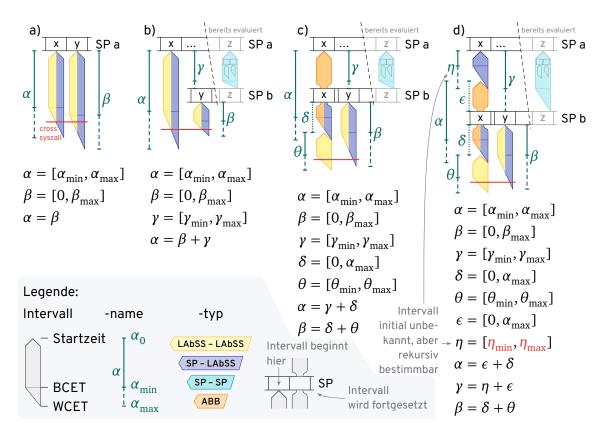

| 7.4   | Die Funktionsweise der MultiSSE im Detail    |

|-------|----------------------------------------------|

| 7.4.1 | Konzepte und Datenstrukturen                 |

| 7.4.2 | Die Initialisierung                          |

| 7.4.3 | Kernlokale Analyse                           |

| 7.4.4 | Synchronisationspartnersuche                 |

| 7.4.5 | SP-Konstruktion und Interpretation           |

| 7.4.6 | Terminierung und Reevaluierungen             |

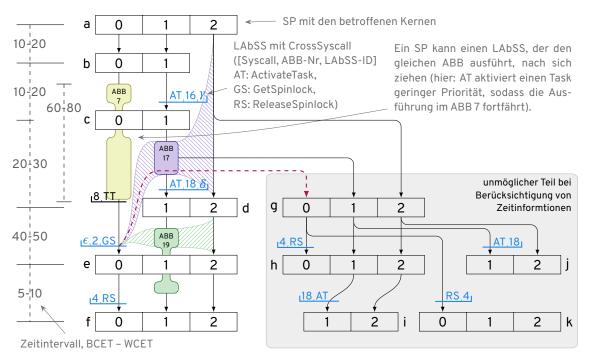

| 7.5   | Berücksichtigung von Zeitinformationen       |

| 7.5.1 | Der Aufbau eines Ungleichungssystems         |

| 7.5.2 | Herausforderungen                            |

| 7.5.3 | Zeitverhalten des Beispielsystems            |

| 7.6   | Externe Interrupts                           |

| 7.7   | Optimierungen                                |

| 7.7.1 | Verhinderung von IPIs                        |

| 7.7.2 | Auslassen überflüssiger Sperren              |

| 7.8   | Evaluation                                   |

| 7.8.1 | Optimierungspotential                        |

| 7.8.2 | Konformitätstests von Trampoline             |

| 7.8.3 | Synthetische Benchmarks                      |

| 7.8.4 | Die Beispielapplikation                      |

| 7.8.5 | Der I4 <i>Copter</i>                         |

| 7.9   | Diskussion                                   |

| 8     | RTOS-Agnostische Analyse                     |

| 8.1   | Echtzeitbetriebssystemschnittstellen         |

| 8.2   | Analyseanforderungen                         |

| 8.3   | Aufbau der <i>Analyse-RTOS-Schnittstelle</i> |

| 8.4   | Evaluation der Betriebssystemmodelle         |

| 3.4.1 | Echtweltanwendungen                          |

| 8.5   | Ergebnisse                                   |

| 8.6   | Diskussion                                   |

|       |                                              |

| 9     | Zusammenfassung 163                          |

| 9.1   | Ausgangssituation                            |

| 9.2   | Forschungsfragen                             |

| 9.3   | Ausblick                                     |

| 9.4   | Fazit                                        |

| _     |                                              |

| ٨     | Anhang 171                                   |

| A.1   | Konkrete Systemaufrufe | 172   |

|-------|------------------------|-------|

| A.1.1 | AUTOSAR                | . 172 |

| A.1.2 | FreeRTOS               | . 172 |

| A.1.3 | Zephyr                 | . 173 |

| A.1.4 | POSIX                  | . 174 |

| A.2   | Verwendete Software    | 174   |

| ۸ 2   | Artofakto              | 175   |

1

# **Einleitung**

# **Motivation und Kontext**

"To be is to do" – Socrates. "To do is to be" – Jean-Paul Sartre. "Do be do be do" – Frank Sinatra.

Kurt Vonnegut aus "Deadeye Dick" (1982), basierend auf einem Graffiti in Richardson, Texas

### 1.1 Motivation

Als John Bardeen, William Shockley und Walter Brattain 1947 den ersten baubaren Bipolartransistor erfanden, schufen sie damit die Grundlagen für eine rapide Verkleinerung der in den folgenden Jahrzehnten entstandenen Rechenmaschinen [BB48,Nob23]. Mithilfe moderner Mikroelektronik ist es inzwischen möglich, alle möglichen Geräte mit programmierbaren Bausteinen auszurüsten, was zu einem Blumenstrauß an programmierbarer Kleinstelektronik geführt hat (z.B. Glühlampen, Kühlschränke, Heizungsthermostate aber auch Assistenzsysteme in Fahrzeugen, Schleusensteuerungen, Signalsysteme), deren Arten alle zu eigen haben, dass das enthaltene Rechensystem keinem Selbstzweck dient, sondern in ein größeres Gerät eingebettet ist. Diese Systeme werden darum eingebettete Systeme genannt [Mar21A1.1]. Eingebettete Systeme stellen einen wachsenden Markt dar, der von einer Marktgröße in 2021 von 39,4 Mrd. USD bis 2027 auf 63,7 Mrd. USD anwachsen soll [Gro22].

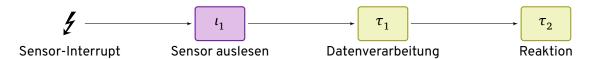

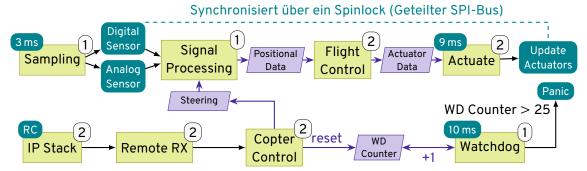

Echtzeitsysteme Eng verwandt mit eingebetteten Systemen sind die Echtzeitsysteme, die dadurch definiert sind, dass sie in einer festgesetzten Zeitspanne ("Frist (Deadline)") reagieren müssen, da andernfalls fatale Folgen eintreten [Liu00A2.3, Kop11A1.1, Die19A2.1]. Diese Systeme kontrollieren beispielsweise Steuerungen wie die Fluglageregelung eines Quadrokopters, der nicht rechtzeitig genug reagieren und abstürzen könnte, wenn er seine Frist nicht einhält. Da Echtzeitsysteme üblicherweise in ein größeres System eingebettet sind, bilden sie eine Unterkategorie innerhalb der eingebetteten Systeme [Kop11A1.6.1,Mar21A1.3].

> Eingebettete Systeme werden von Software gesteuert, der Anwendung, die oftmals ein Betriebssystem als Hilfsbibliothek benutzt. Um auch Echtzeitsystemen gerecht zu werden, sind dies oftmals Echtzeitbetriebssysteme.

(nicht-) Zur Erfüllung ihrer Aufgabe müssen eingebettete Systeme eine spezifizierte Menge an funktionale Eigenschaften erfüllen, die funktionalen Eigenschaften. Ebenso große Bedeutung haben Eigenschaften aber auch die nichtfunktionalen Eigenschaften, eine Menge aller Eigenschaften, die für die korrekte Erfüllung der Aufgabe irrelevant sind, wie z.B. der Speicherverbrauch, der Energieverbrauch oder die Anwendungsgröße [Loh14A6.1,Die19A2.1]. Diese werden maßgeblich durch die Software beeinflusst, beschränken aber entweder die verwendbare Hardware ("dieser Microchip ist nicht stark genug") oder beeinflussen maßgeblich das Benutzererlebnis. So finden oftmals Firmwareupdates ein größeres Presseecho, die nichtfunktionale Eigenschaften wie die Akkulaufzeit verbessern [Gar22,App22].

Maß- Verbesserungen der nichtfunktionalen Eigenschaften werden oftmals durch Maßschneischneiderung derung erreicht: Die Software wird konkret auf die Hardware angepasst, verwendet deren Spezialinstruktionen (z.B. gesonderte Vektoroperation), vermeidet überflüssige Anweisungen (z. B. das Initialisieren überflüssiger Hardware) oder inkludiert bereits vorausberechnete Ergebnisse (z. B. ausgerechnete Konstanten) [ALS+08A1.2.5+9+11,Loh14A1]. Ein großer Teil dieses Prozesses ist mühsam, immer gleich und eignet sich hervorragend zum Automatisieren. Dies wurde schon in den Sechzigern erkannt, als mit dem IBM Fortran H einer der ersten optimierenden Compiler vorgestellt wurde (nur sechs Jahre nach der Vorstellung der Sprache Fortran selbst) [SK80].

Eingebettete Systeme haben meistens durch ihre Einbettung eine vor ihrer Inbetriebnahme festgelegte Aufgabe [Mar07A1.1]. Um die Aufgabenerfüllung gewährleisten zu können, muss auch die gesamte Software, die auf dem Gerät laufen wird, bereits zu dieser Zeit bekannt sein. Dementsprechend gut eignet sich Software für eingebettete Systeme für eine Whole-Program-Optimization, also eine Optimierung, die das System im Gesamten berücksichtigt [BEG+07]. Ein spezieller Teilbereich dieser Optimierung beschäftigt sich dabei mit der Maßschneiderung des Betriebssystems auf die Anwendung. Mit dOSEK [HLD+15b,DHL17] oder dem RTSC [SS10] existieren z.B. zwei Whole-System-Compiler, die durch Entfernung von Systemaufrufen, Vorberechnung der Scheduling-Entscheidungen oder Aufteilen auf mehrere Kerne das Gesamtsystem beschleunigen und verkleinern können.

Die grundlegende Architektur ist dabei bei allen Übersetzern gleich: Einer jeden Optimie- statische rung geht ein entsprechender Analyseschritt voraus, der die notwendigen Informationen Analyse automatisch extrahiert und damit die Optimierung überhaupt ermöglicht. Da diese Analyse das zu übersetzende Programm nicht ausführt, sondern Rückschlüsse dadurch zieht, den Programmtext zu betrachten, wird sie statische Analyse genannt [RY20A1.3.2].

Die oben genannten Übersetzer sind auf den OSEK-Echtzeitbetriebssystemstandard zugeschnitten, der von der Anwendung verlangt, alle Betriebssystemobjekte statisch (also vor der Laufzeit) festzulegen, nur auf Einkern-Systemen läuft und genau ein Scheduling-Modell unterstützt [OSE05]. All dies kommt der Analyse in den Übersetzern zugute, die dadurch auf einer Betriebssystemschnittstelle operieren können, bei der bereits große Teile des Systemverhaltens zur Übersetzungszeit festgeschrieben sind.

Die Verfahren verlieren aber dadurch an Allgemeingültigkeit: Im Gegensatz zu OSEK ist bei- Dynamische spielsweise im Echtzeitbetriebssystem Zephyr sowohl eine statische als auch eine dynami- Betriebssysteme sche Erstellung von Betriebssystemobjekten möglich [Pro23b]. Das Echtzeitbetriebssystem FreeRTOS wiederum lässt nur die dynamische Konfiguration zu [Ama23]. Die Analyse nur auf statische Betriebssysteme auszulegen, verhindert damit bereits konzeptuell die Untersuchung von Anwendungen für andere Betriebssystemschnittstellen, die aber gerade in der eingebetteten Domäne ebenso verwendet werden<sup>1</sup>.

OSEK ist 2003 im AUTOSAR-Standard aufgegangen, der das Betriebssystem um parti- Mehrkerntionierte Mehrkernfähigkeit erweitert [AUT13]. Mehrkernunterstützung ist in anderen systeme Bereichen (Server, HPC, Desktop [TOP23, Val23]) längst angekommen und wird auch

<sup>&</sup>lt;sup>1</sup> Nach [EA19] ist Linux (POSIX) das am häufigsten eingesetze Betriebssystem im eingebetteten Bereich gefolgt von FreeRTOS, beide vollständig dynamisch.

für eingebettete Systeme immer wichtiger. So haben von den 133 ARM basierten SoCs von Texas Instruments (für eingebettete Systeme der beliebteste Prozessorhersteller [EA19]) 86 der Hauptprozessoren mehrere Kerne oder zumindest einen oder mehrere Coprozessoren [Inc23]. Gerade im Bereich der Echtzeitsysteme fehlen aber passende Analysen. Das Hauptproblem dabei ist der fehlende Determinismus der Kerne zueinander. Konkret ist unklar, an welcher Position ein Kern im Vergleich zu den anderen ist. Die naive Lösung dieses Problems ist die Berechnung des Kreuzproduktes aller Kernpositionen, die jedoch durch ihr exponentielles Wachstum praktisch ungültig ist [Min12]. In bisherigen Ansätzen wurde darum die Flusssensitivität für den Interaktionsbereich aufgegeben [Min12] oder modellbasiert gearbeitet [HBR21,HBR22,MB21]. Diese Ansätze verwerfen allerdings Informationen, um skalierbar zu sein.

Betriebssystem- Die Übersetzer RTSC und dOSEK, aber auch andere betriebssystemgewahre Analyseprospezifische gramme wie GOBLINT [VV09] unterstützen nur eine Betriebssystemschnittstelle. Dies be-Analyse schränkt die implementierten Algorithmen zwar konzeptuell nicht zwangsläufig auf genau dieses Betriebssystem, praktisch aber oft schon. Es birgt außerdem die Gefahr, den Algorithmus auf bestimmte Konzepte des Betriebssystems anzupassen, ihn dadurch aber auch davon abhängen zu lassen. Die später vorgestellte SSE-Analyse [DL17], die von dOSEK implementiert wird, ist beispielsweise inhärent nur auf statische Systeme anwendbar.

## 1.2 Forschungskontext

Methodik der Diese Arbeit findet im Forschungskontext des DFG-Projektes "Automated Hardware Abs-Spezialisierung traction in Operating-System Engineering" (LO 1719/4-1) statt. Ziel des Projektes ist die Grenzen möglichst automatischer Maßschneiderung bzw. Spezialisierung des Betriebssystems und ggf. auch der darunterliegenden Hardware auf eine vorgegebene Anwendung eines eingebetteten Systems auszuloten. Dabei geht es zum einen darum, einen möglichst hohen Grad der Maßschneiderung zu erreichen, diesen aber anschließend auch variieren zu können. Der grundlegende Gedanke lässt sich in folgender Formel zusammenfassen [>FED+18]<sup>2</sup>:

$$RTS(\vec{1}) = \vec{O} \stackrel{RTS}{=} RTS \stackrel{A}{=} RTS \stackrel{A}{=} (\vec{1})$$

Wir gehen dabei von einer Spezifikation für ein Echtzeitsystem (Real-Time System, RTS) aus, das eine Menge von Eingabeereignissen I erhält und auf diese mit einer definierten Ausgabe O reagieren soll. Die Spezifikation kann nun von einer konkreten Implementierung  $RTS_{\text{line}}^{\text{RTS}}(\vec{1})$  erfüllt werden. In diesem Fall gilt der spezielle Gleichheitsoperator  $\vec{R}_{\text{res}}^{\text{RTS}}$ , der eine Implementierung mit der Spezifikation vergleicht. Die konkrete Implementierung besteht

<sup>&</sup>lt;sup>2</sup> Ich gehe hier nur kurz auf die Formel ein. Mein Kollege Björn Fiedler beschreibt sie deutlich detaillierter in seiner Dissertation [Fie23A2.2].

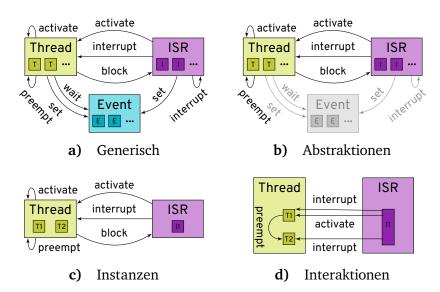

Abbildung 1.1 Die verschiedenen Optimierungslevel für eingebettete Systemsoftware. Das generische Level beschreibt die vollständige unoptimierte Betriebssystemschnittstelle. Bei b) kann auf der Ebene ganzer Betriebssystemabstraktionen spezialisiert werden. c) beschreibt die Spezialisierung einzelner Instanziierung von Betriebssystemobjekten, während im Level d) die genauen Interaktionen zwischen Instanzen flusssensitiv bekannt sind und spezialisiert werden können (adaptiert aus [›FED+18]).

aus einer Anwendung (A), einem Echtzeitbetriebssystem (Real-Time Operating System, RTOS) und einer unterliegenden Hardware (HW). Für alle diese Komponenten gilt: Sie können beliebig angepasst (maßgeschneidert) werden, solange sie der Spezifikation entsprechen, also die Gleichheit erfüllt bleibt.

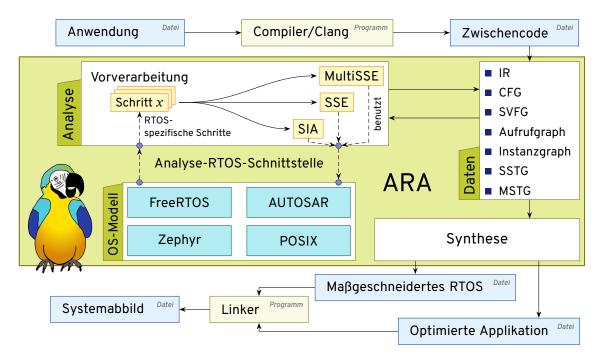

Ziel des Forschungsprojektes ist die automatische Maßschneiderung. Konkret haben wir automatische dazu einen Whole-System-Compiler entwickelt, der als Eingabe eine Implementierung Spezialisierung einer Anwendung in einer Hochsprache als Spezifikation annimmt und daraus ein maßgeschneidertes konkretes System RTS we erzeugt. Auch hier gliedert sich der Mechanismus in eine Synthese und eine vorhergehende Analyse, bei der grundsätzlich gilt, dass sie die für die Synthese notwendigen Informationen liefern soll. In dieser Dissertation werde ich auf die Analyse eingehen. Die verschiedenen Synthesen hat zum einen Björn Fiedler in seiner Dissertation erarbeitet [Fie23] und zum anderen Andreas Kässens für seine in Arbeit befindliche Dissertation.

Generell gilt für die Analyse, dass sie alle Informationen liefern muss, die die Synthese Grade der benötigt, also insbesondere auch eine Übermenge an Informationen liefern kann. Wir Spezialisierung haben daher als Teil des Projektes ebenfalls eine Klassifikation an Spezialisierungsgraden (und damit auch Analysegraden) erstellt, die in Abbildung 1.1 dargestellt ist:

Grad der Abstraktionen: Jedes Betriebssystem bietet eine Fülle von Abstraktionen, wie Fäden, Semaphoren oder Signale. Je nach Anwendung werden diese Abstraktionen aber nie verwendet, was zur Optimierung genutzt werden kann. Wenn eine automatisierte Analyse feststellt, dass eine Anwendung eine Abstraktion nie verwendet, kann diese für die Anwendung vollständig aus dem Betriebssystem ausgebaut werden [TKH+12, RHL14].

Grad der Instanzen: Viele Betriebssystemabstraktionen können instanziiert werden. Die Optimierung hier gilt dann für diese konkreten Instanzen oder ihre (flussinsensitiven) Interaktionsmuster. Stellt eine Analyse dabei z. B. fest, dass genau zwei instanziierte Fäden einmal ausschließlich lesend und einmal ausschließlich schreibend auf eine bestimmte instanziierte geteilte Liste zugreifen, kann die dahinterliegende Datenstruktur entsprechend optimiert werden [Fie23A5.1]. Es gibt weitere Optimierungen, die Speicher einsparen oder die Robustheit gegen Angriffe erhöhen [HBD+14,HLS+09,HDM+12].

Grad der Interaktionen: Die Instanzen, z.B. zwei Fäden, interagieren miteinander an fest definierten Stellen im Programmkontrollfluss: den Systemaufrufen. Eine Analyse kann hier beispielsweise feststellen, dass das Senden eines Signals an einer definierten Stelle im Kontrollfluss immer dazu führt, dass ein ganz bestimmter Faden aufgeweckt und zudem eingeplant wird. In diesem Fall kann diese Planungsentscheidung in das System fest eincodiert werden und so die Zeit senken, die das Betriebssystem zur Berechnung braucht [DHL17].

Der hier vorgestellte Grad ist ansteigend, sodass eine Analyse, die Interaktionsinformationen liefert, automatisch auch Synthesen ermöglicht, die Abstraktions- oder Instanzinformationen benötigen. Bisherige Werkzeuge lassen sich in die oben beschriebenen Kategorien einsortieren, sind aber entweder auf ein spezielles Betriebssystem zugeschnitten oder konzentrieren sich auf spezielle Optimierungen. Zentraler Punkt des Forschungsprojektes ist im Gegensatz dazu eine Vergleichbarkeit verschiedener Methoden zu schaffen, die es ermöglicht, mit dem gleichen Werkzeug Systeme verschiedener Betriebssysteme auf gleiche Art zu optimieren bzw. ein System in verschiedenen Arten bzw. Graden zu optimieren. Ein wichtiger Baustein ist dabei die optimale Ausnutzung von Mehrkernsystemen, insbesondere bei der Optimierung auf Basis von Interaktionen, da diese kein Bestandteil vorheriger Arbeiten sind. Ich habe in dieser Dissertation die Grundlagen für eben diese Vergleichbarkeit gelegt, indem ich ein Analyse-Framework geschaffen habe, das betriebssystemagnostisch Systeme in verschieden Graden und auch Mehrkernsysteme analysieren kann.

### 1.3 Zweck dieser Arbeit

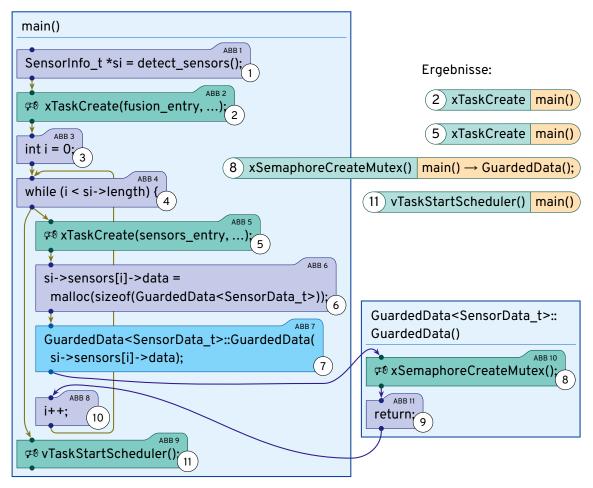

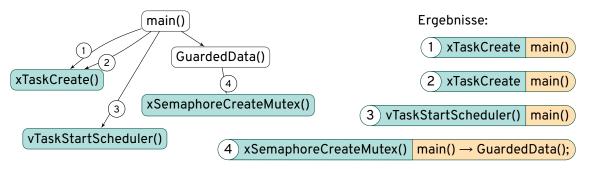

Anwendung zur Um die Problematik etwas plastischer darzustellen, will ich etwas vorgreifen und ein Demonstration Beispielsystem mit möglichen Optimierungen zeigen, die in verwandten Arbeiten nicht

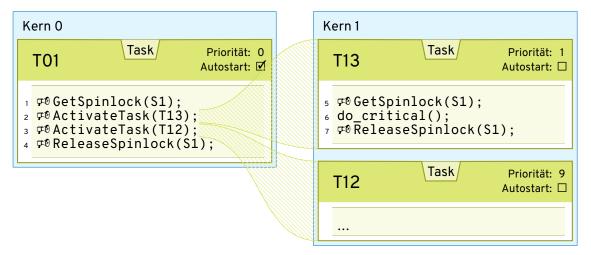

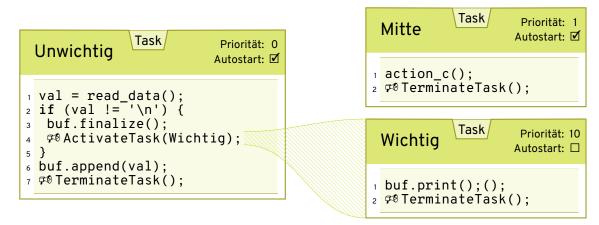

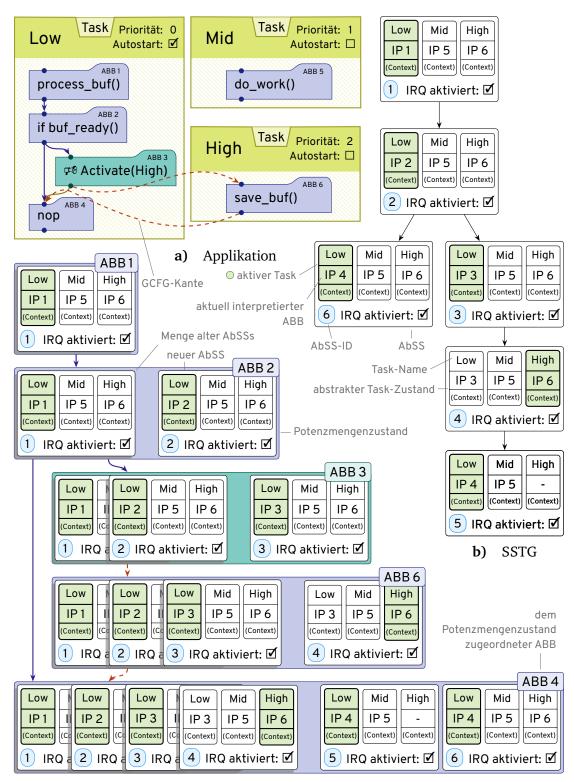

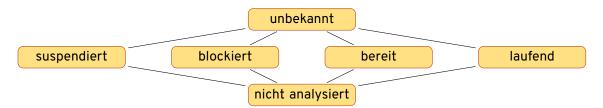

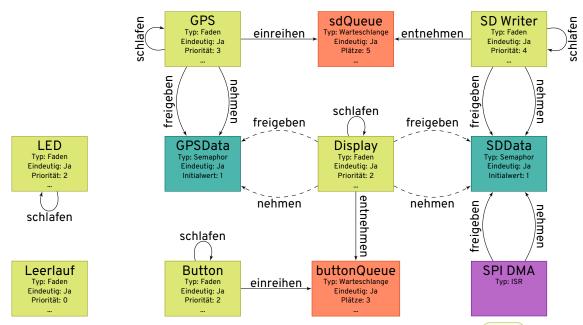

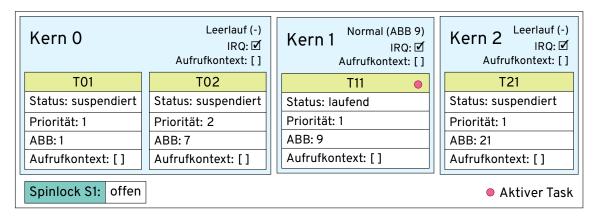

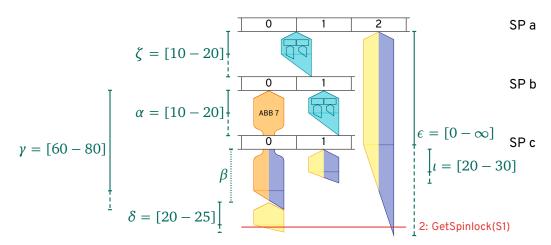

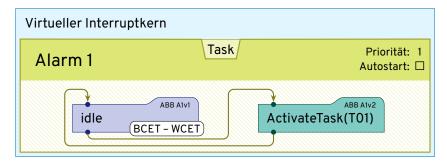

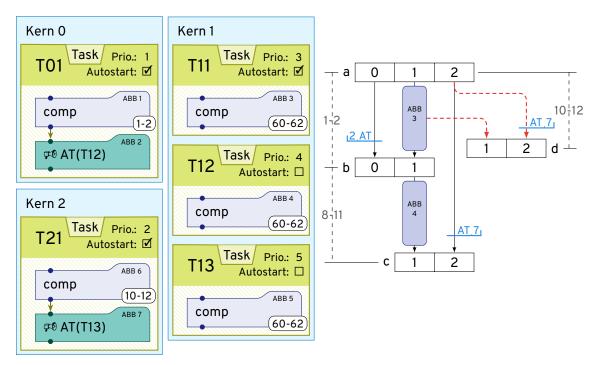

Abbildung 1.2 Eine Echtzeitanwendung, die mithilfe der Echtzeitbetriebssystemschnittstelle AUTOSAR geschrieben wurde. Zu sehen sind drei AUTOSAR-Tasks (Fäden) verschiedener Priorität (eine größere Zahl ist höherprior), die auf zwei Kernen laufen. *T01* startet beim Systemstart und aktiviert ("setzt lauffähig") anschließend die beiden anderen. ActivateTask(T12) wird in dieser Anwendung niemals ein Umplanen ("Reschedule") auslösen und braucht deswegen keinen Inter-Prozessor-Interrupt.

| Eigenschaft                    | dOSEK        | RTSC         | GOBLINT      | Astrée       | ARA          |

|--------------------------------|--------------|--------------|--------------|--------------|--------------|

| Mehrkernunterstützung          | ×            | ×            | ✓            | ✓            | $\checkmark$ |

| Betriebssystemagnostisch       | ×            | ×            | ×            | $\checkmark$ | $\checkmark$ |

| Dynamisches System             | X            | ×            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Quelloffen                     | $\checkmark$ | $\checkmark$ | $\checkmark$ | ×            | $\checkmark$ |

| Für Maßschneiderung (Compiler) | $\checkmark$ | $\checkmark$ | ×            | ×            | $\checkmark$ |

**Tabelle 1.1** Vergleich verschiedener betriebssystemgewahrer statischer Analysen

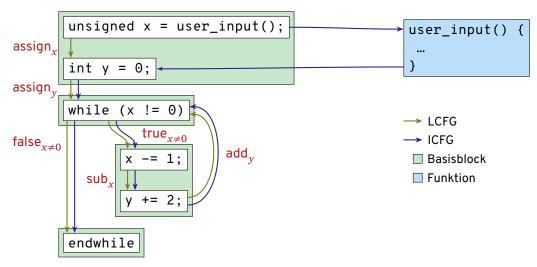

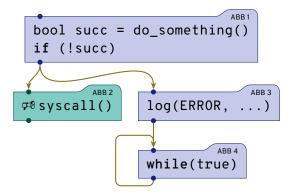

existieren. Abbildung 1.2 zeigt dazu eine Echtzeitanwendung, die für ein Zielsystem mit zwei Kernen und auf Basis der AUTOSAR-Echtzeitbetriebssystemschnittstelle geschrieben wurde. Konkret aktiviert der Task *T01* auf Kern 0 hier den Task *T13*, der daraufhin vom ersten Kern parallel ausgeführt wird. Dadurch, dass anschließend die Sperre von Task *T01* gehalten wird, ist Task *T13* in jedem Fall noch am Laufen, wenn Task *T12* aktiviert wird. Der Betriebssystemstandard schreibt in diesem Fall vor, dass – wenn nötig – ein Neuplanen auf allen Kernen ausgeführt werden muss. Dazu muss der entsprechende Kern benachrichtigt werden, was in einem teuren Inter-Prozessor-Interrupt resultiert [HCK+03, EKF+24]. Mit der geeigneten Analyse kann gezeigt werden, dass dieser Interrupt überflüssig ist und entsprechend optimiert werden kann. Die Analyse, die dieses Wissen extrahiert, muss einerseits die Systemaufrufe der Betriebssystemschnittstelle interpretieren, andererseits

korrekte Rückschlüsse über das Scheduling-Verhalten ziehen und zuletzt auch noch über die Interaktionen zwischen den Kernen schlussfolgern können. Sie muss außerdem den Kontrollfluss innerhalb des Kerns und die Systemaufrufwerte korrekt erkennen.

Forschungsfragen Mit dieser Dissertation habe ich ein Framework – ARA – geschaffen, dass alle diese Analyseaufgaben erfüllt, verschiedene Analysegrade zulässt und alle Analysen überdies betriebssystemagnostisch ausführt. Mit diesem Framework will ich die oben genannten Probleme angehen: Mehrkernfähigkeit für Optimierung nicht gegeben, Einschränkung der Analyse auf statische Betriebssysteme, Vergleichbarkeit von mehreren Betriebssystemen nicht möglich. Konkret führen mich diese Probleme zu den folgenden Forschungsfragen.

#### Forschungsfrage 1: Welche Herausforderungen entstehen auf eingebetteten dynamischen Systemen und können betriebssystemgewahre Analysen diese überwinden?

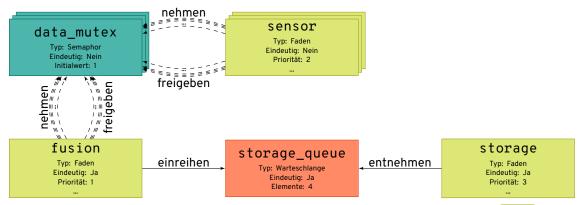

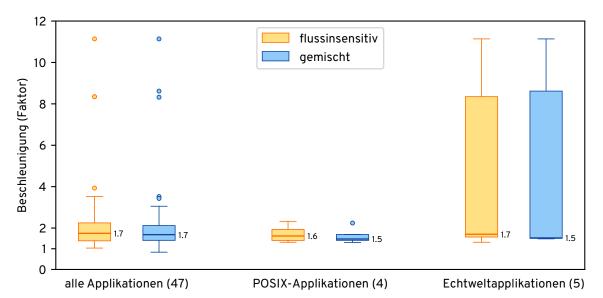

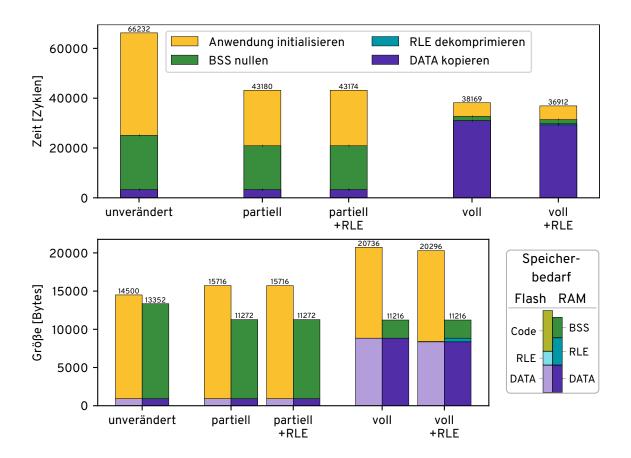

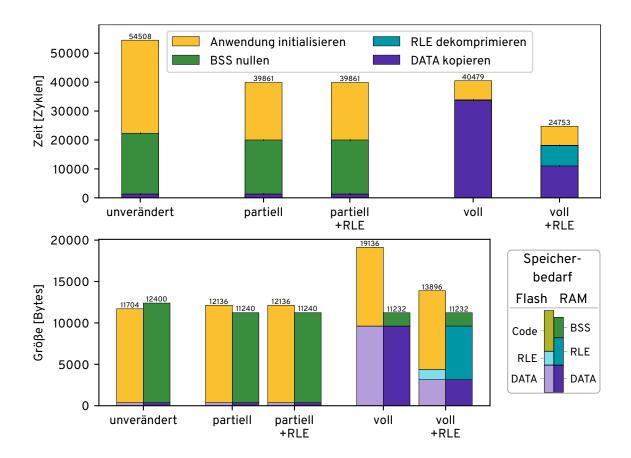

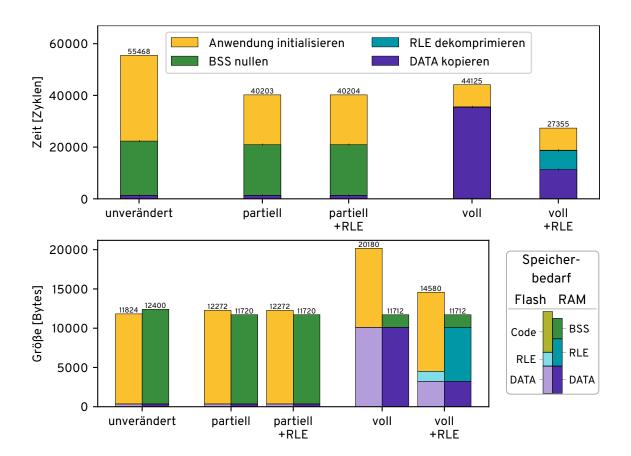

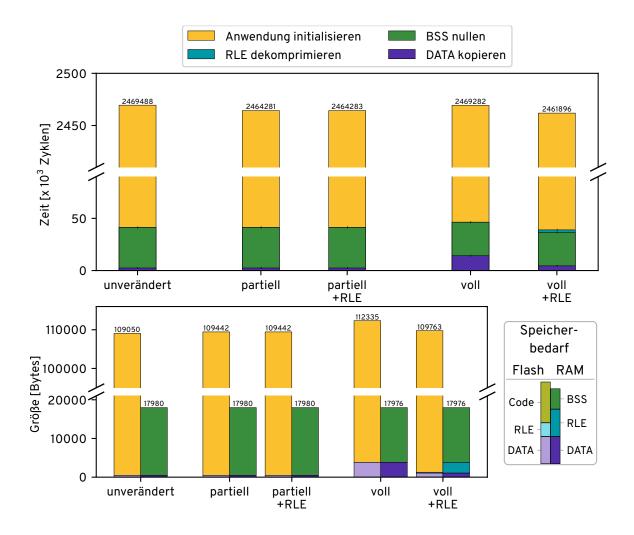

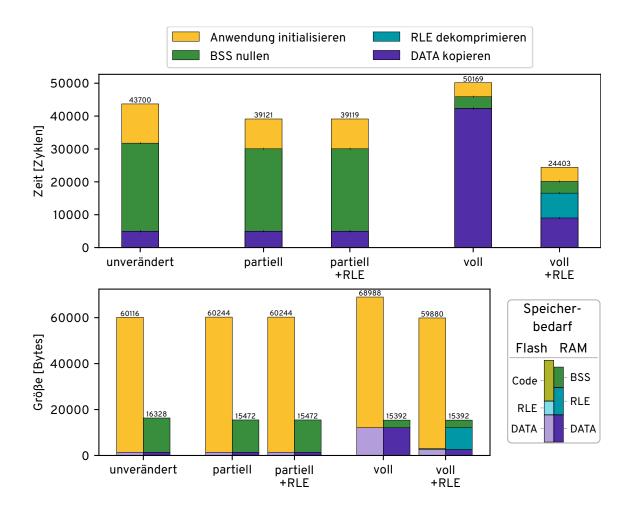

Forschungsergebnis: Ich habe zur Beantwortung dieser Frage die statische Instanzanalyse (Static Instance Analysis, SIA) entwickelt, die eine betriebssystemgewahre Analyse für dynamische Systeme darstellt und dort konkret Instanzen von Betriebssystemobjekten und deren Interaktionen (in einer flussinsensitiven Darstellung) extrahiert. Die SIA ihrerseits gliedert sich in ein flusssensitives und flussinsensitives Verfahren auf, die sich hinsichtlich Präzision und Komplexität unterscheiden, zusammen mit einem kombinierten Verfahren, das die Vorteile beider vereint. Sie liefert dabei Ergebnisse auf Ebene der Instanzspezialisierung, analysiert den Code aber wahlweise auf Ebene der Interaktionen. Die Resultate der SIA konnten Björn Fiedler und ich zusammen mit einer passenden Synthese evaluieren und eine Verringerung der Startgeschwindigkeit von 44% erreichen.

Relevante Veröffentlichung: [>FED+21]

#### Forschungsfrage 2: Ist eine betriebssystemgewahre abstrakte Interpretation auf Mehrkernsystemen ohne Potenzmengenbildung durchführbar?

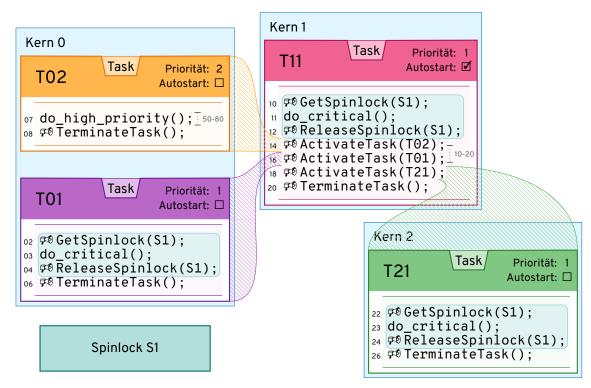

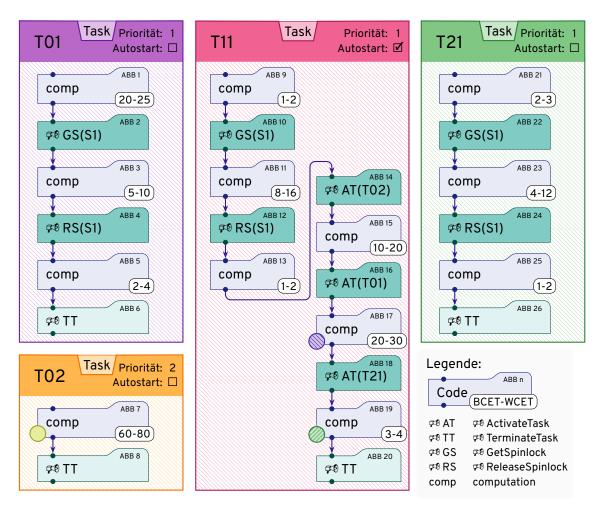

Forschungsergebnis: Diese Forschungsfrage konnte ich durch die Entwicklung der Multi-SSE bejahen. Die MultiSSE setzt die abstrakte Interpretation für Mehrkernsysteme um, umgeht die Potenzmengenbildung aber durch die Zustandstrennung in Zustände, die von anderen Kernen unabhängig auf einem singulären Kern auftreten und expliziten Synchronisationspunkten, die zwei oder mehrere Kerne in ihrer zeitlichen Relation zueinander determinieren. Mithilfe der MultiSSE konnte ich zusätzliche Optimierungen finden, die nur im Kontext von Mehrkernsystemen Sinn ergeben, aber auf der Ebene von Interaktionen spezialisieren, also auch eine solche Analyse voraussetzen.

Relevante Veröffentlichung: [>EFL23,>EKF+24]

#### Forschungsfrage 3: Welche Gemeinsamkeiten und Unterschiede haben Echtzeitbetriebssystemschnittstellen und wie kann man Analysen davon unabhängig machen?

Forschungsergebnis: Um Gemeinsamkeiten und Unterschiede der bestehenden und neu geschaffenen Analysen aufzuzeigen, habe ich diese (erstmals) in einen theoretischen Kontext gebettet. Mit einer zusätzlichen Klassifizierung der Echtzeitbetriebssystemschnittstellen in analyserelevante Faktoren konnte ich eine *Analyse-RTOS-Schnittstelle* entwickeln, die Analysen und Betriebssystemschnittstellen trennt. All das konnte ich so in ein gemeinsames Framework – ARA – einbetten, das damit betriebssystemagnostisch statische betriebsystemgewahre Analysen durchführen kann. Innerhalb des Frameworks schaffen konkrete Implementierungen der Schnittstelle für AUTOSAR, FreeRTOS, Zephyr und POSIX die Unterstützung für Anwendungen auf Basis dieser Systeme, was ich mit der Analyse von 8 Echtweltanwendungen nachweisen konnte.

Relevante Veröffentlichungen: [>ESD19,>ENL22]

### 1.4 Aufbau der Arbeit

Die Arbeit besteht aus zwei Teilen: Im Teil I: "Grundlagen" stelle ich bestehende Techniken vor und ordne diese in einen theoretischen Kontext ein. Der Teil gliedert sich dazu in vier Kapitel:

Kapitel 2: "Eingebettete und Echtzeitsysteme" gibt einen Einblick in meine Forschungsdomäne. Dieses Kapitel stellt die wichtigsten Konzepte aus dem Bereich und auch die konkreten Echtzeitbetriebssystemschnittstellen vor, die in dieser Arbeit Verwendung finden.

Kapitel 3: "Statische Analyse" gibt einen Einblick in meine Forschungsmethode. Es wird die theoretischen Grundlagen der in dieser Arbeit verwendeten Analysen vorstellen und allgemeine Vorteile und Herausforderungen herausarbeiten.

Kapitel 4: "Betriebssystemgewahre Analyse" verbindet Methode und Domäne zum Mechanismus der betriebssystemgewahren Analyse und stellt den aktuellen Stand der Kunst auf diesem Bereich vor. In diesem Kapitel werde ich weiterhin einige vorhandene Analysen theoretisch einordnen und damit einen Baustein zur Beantwortung der 3. Forschungsfrage liefern.

Kapitel 5: "ARA" stellt alle Teile des neu geschaffenen ARA-Frameworks vor, die für die eigentlichen betriebssystemgewahren Analysen notwendig sind, aber bereits bestehende Verfahren verwenden.

Anschließend geht der Teil II: "Konzepte" detailliert mit drei Kapiteln auf meine Forschungsfragen und die dafür neu geschaffenen Analysen ein:

Kapitel 6: "Statische Analyse dynamischer Systeme" stellt die *statische Instanzanalyse (Static Instance Analysis, SIA)* vor, eine Analyse, die ich zur Beantwortung meiner 1. Forschungsfrage geschaffen habe und zeigt deren Evaluation an zwei Echtweltsystemen.

Kapitel 7: "Die Analyse von Mehrkernsystemen" geht auf die MultiSSE ein, eine Analyse, die die 2. Forschungsfrage beantwortet, zeigt deren Funktionsweise zeigt, stellt eine Synthese auf ihrer Basis vor und evaluiert und diskutiert die Analyse anschließend.

Kapitel 8: "RTOS-Agnostische Analyse" gliedert die SIA und MultiSSE anschließend in ARA ein und macht diese unabhängig vom konkreten RTOS. Es beantwortet dabei meine 3. Forschungsfrage.

Im Kapitel 9: "Zusammenfassung" fasse ich abschließend meine Forschungsergebnisse zusammen und gebe einen kleinen Ausblick.

# 1.5 Typographische Konventionen

Um Patterson and Hennessy zu zitieren [PH21A1.1]:

Computer Designers (including the authors) love using acronyms, which are easy to understand once you know what the letters stand for!

Aus diesem Grund ist selbstverständlich auch diese Arbeit gespickt von Akronymen. Diese sind aber oft eine Abkürzung für die englischen (Original-)Begriffe. Ich werde daher bei Akronymen immer die englische Version verwenden, aber die deutsche Variante für die Langversion<sup>3</sup>. Bei der Einführung eines Begriffs werde ich sowohl die deutsche als auch englische Version nennen.

Literaturreferenzen sind in eckigen Klammern gesetzt. Sollten diese auf Bücher, Dissertationen und Habilitationen verweisen, sind diese gesondert mit einer Abschnittsmarkierung versehen, wo in dem entsprechenden Werk die gewünschte Information aufzufinden ist, z. B. befindet sich bei [Mar21A1.1] die Referenz in dem Buch "Embedded System Design: Embedded Systems Foundations of Cyber-Physical Systems, and the Internet of Things" von Peter Marwedel in Abschnitt 1.1. Referenzen zu bereits veröffentlichten Arbeiten, bei denen ich Coautor bin, sind zusätzlich mit "" gekennzeichnet (z. B. [›ENL22]).

Einige Konzepte sind gesondert gesetzt:

- "🕫 system\_aufruf()" ist ein Systemaufruf (Definition 4).

- "T01" und "GPSQueue" kennzeichnen Instanzen (Definition 2).

- "CALL" ist ein Typ eines Atomaren Basisblocks (Definition 18).

- "main" ist eine Funktion.

$<sup>^3</sup>$  Manche deutschen Fachwörter erscheinen ungewohnt. Ich habe mich hier an Schröder-Preikschat orientiert [Sch19].

# Teil I Grundlagen

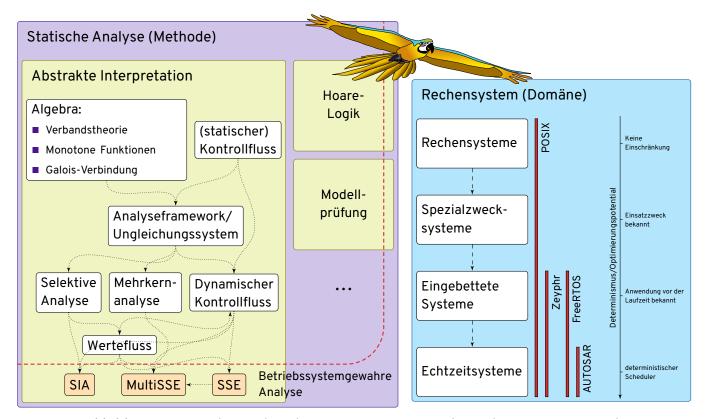

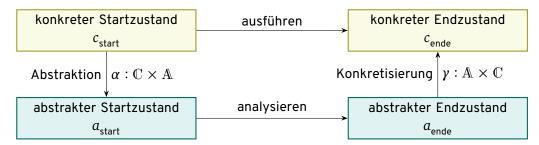

Diese Arbeit kombiniert die Methode der statischen Analyse mit der Domäne der eingebetteten Echtzeitsysteme. Abbildung 3 stellt die Inhalte des Grundlagenteils in seiner Gesamtheit dar. Die statische Analyse ist eine Methode, um Informationen aus Systemen zu extrahieren, *ohne* diese auszuführen [RY20A1.3.2]. Je nach gewünschten Informationen gibt es eine Vielzahl von Analysen von unterschiedlichen Laufzeiten und Komplexitäten. In dieser Arbeit werde ich mich mit dem Teilgebiet der *abstrakten Interpretation* beschäftigen [CC77]. Diese verwende ich dazu, Anwendungen eingebetteter Systeme hinsichtlich der Verwendung des Betriebssystems zu untersuchen.

Eingebettete Echtzeitsysteme sind Rechensysteme, die in ein sie umgebendes System eingebettet sind. Sie haben darum einen festen Einsatzzweck und einen Fokus auf Zuverlässigkeit und Sicherheit [Mar21A1.1]. Ersterer gestattet und letztere erfordern ein möglichst deterministisches Design, das diese Systeme analysierbar macht.

Ich werde in diesem Teil zuerst eingebettete Systeme (Kapitel 2) und die allgemeine Technik der statischen Analyse vorstellen (Kapitel 3). Anschließend werde ich auf den Stand der Kunst eingehen, beide zu kombinieren (Kapitel 4). In Kapitel 5 geht es schlussendlich um das ARA-Framework – die konkrete Anwendung und Adaptierung der davor angesprochenen Konzepte, die die Grundlage für die im nächsten Teil vorgestellten Analysen bildet.

Abbildung 3 Einordnung abstrakter Interpretationen und eingebetteter Systeme. Ich arbeite mit der Methode der statischen Analyse auf der Domäne der eingebetteten Systeme. Beide Bereiche werden durch das ARA-Analyse-Framework verbunden. Die statische Analyse gliedert sich in mehrere verschiedene Verfahren auf, von denen ich mit der abstrakten Interpretation gearbeitet habe [CC77]. Beachtet man die Domäne als Eigenschaft der statischen Analyse, erhält man das (querschneidende) Teilgebiet der betriebssystemgewahren Analyse, bei der die schon existierende konkrete Analyse SSE [DL17] und die mit dieser Arbeit neu entwickelten Analysen SIA [>FED+21] und MultiSSE [>EFL23] in den Bereich der abstrakten Interpretation fallen. Innerhalb der abstrakten Interpretation gibt es umfangreiche (theoretische und praktische) Vorarbeit, die sich in verschiedenen aufeinander aufbauenden Analyseverfahren manifestieren, bei denen die betriebssystemgewahren Analysen letztlich an der Spitze stehen. In der Domäne der Rechensysteme kann eine Hierarchie gefunden werden, bei der die Echtzeitsysteme die am meisten beschränkte, aber dadurch am besten optimierbare Variante darstellen. Für Rechensysteme existieren eine Vielzahl von Betriebssystemen bzw. Betriebssystemschnittstellen, die jeweils einer entsprechenden Untermenge dieser Varianten zugeordnet werden können. In dieser Arbeit werde ich mich auf vier dieser Betriebssystemschnittstellen konzentrieren, von denen POSIX die allgemeinste und AUTOSAR die spezialisierteste Variante darstellt.

# Eingebettete und Echtzeitsysteme

# Konzepte und ihre Ausprägung

Die Latenz in definierten Grenzen zu sichern, kennzeichnet die Echtzeitfähigkeit eines Systems. Es wäre also besser von einem "Rechtzeitsystem" zu sprechen.

Dr.-Ing. Claus Kühnel [Küh17]

Die in dieser Arbeit vorgestellten statischen Analysen sind für eingebettete Systeme ausgelegt. Eine Unterkategorie dieser Systeme sind Echtzeitsysteme. Zur Anwendungsentwicklung wird für beide oft ein Echtzeitbetriebssystem verwendet.

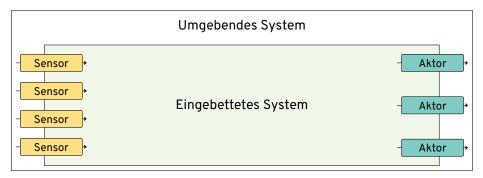

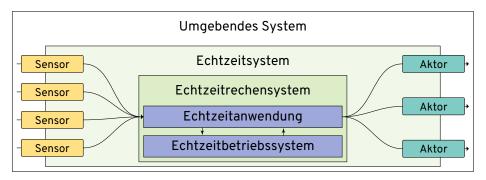

**Abbildung 2.1** Ein eingebettetes System (Schema). Das eingebettete System ist Teil eines es umgebenden Systems und mit diesem über Sensoren und Aktoren verbunden (nach [Die19A2.1]).

### 2.1 Eingebettete Systeme

Bei Rechnersystemen denken wir oft an *Personal Computers (PCs)*, Laptops, Handys und ggf. auch noch Server. Wir benutzen und bedienen diese Systeme direkt. Wir führen dort Programme aus oder wir installieren neue. Wir benutzen das System, um etwas mit diesem System zu machen.

Der deutlich größere Teil an Rechensystemen wird allerdings in andere Geräte eingebettet, um diese in ihrer Funktionalität zu erweitern. Sie sind dadurch für gewöhnlich nicht direkt sichtbar (manchmal auch mit dem Begriff der "verschwindenden Computer" bezeichnet [Mar07A1.1]) und werden indirekt und nur noch als Teil des größeren Systems benutzt. Diese Systeme heißen *Eingebettete Systeme*.

### **Definition 1: Eingebettete Systeme.**

Eingebettete Systeme sind Systeme, die Informationen verarbeiten und in sie umgebende Produkte eingebettet sind (aus dem Englischen übersetzt) [Mar21A1.1].

Sie sind dabei aber vollwertige Rechner, gekennzeichnet durch eine Ausführungseinheit (CPU), Arbeitsspeicher (RAM) und Festspeicher (Flash).

Sinn der Rechensysteme ist oft die Steuerung der sie umgebenden Systeme. Dafür sind sie mithilfe von Sensoren und Aktoren mit diesen verknüpft. Abbildung 2.1 zeigt ein eingebettetes System schematisch<sup>4</sup>.

Verbreitung

Eingebettete Systeme finden sich in nahezu allen größeren technischen Geräten, z.B. in Automobilen, Flugzeugen, smarten Glühbirnen und Industrieanlagen. Sie bilden bei weitem den größten Anteil an Rechensystemen. So kam ein Acatech-Report<sup>5</sup> von 2011 zu dem

<sup>&</sup>lt;sup>4</sup> Manchmal lesen eingebettete Systeme auch nur Daten, ohne zu steuern. In diesem Fall entfallen die Aktoren.

<sup>&</sup>lt;sup>5</sup> Deutsche Akademie der Technikwissenschaften

Schluss, dass eingebettete Mikroprozessoren zu diesem Zeitpunkt einen Marktanteil von 98% ausmachen [Deu11].

Obwohl die Hardware eingebetteter Systeme alle Komponenten eines vollwertigen Computers besitzt, sind die Anforderungen an Hard- und Software ganz andere, da zum einen der Zweck des Systems im Vorhinein feststeht und das System zum anderen möglichst lange unverändert laufen soll.

Vor allem folgende Anforderungen können identifiziert werden [Mar21A1.3,Kop11A1.4]: Anforderungen

**Zuverlässigkeit:** Eingebettete Systeme sollen sicher sein (vor Ausfällen, aber auch vor Angriffen), gut reparierbar und hoch verfügbar. Ein Ausfall eines eingebetteten Systems kann das umgebende System zu einer Fehlfunktion verleiten und damit fatale Folgen provozieren. Ein tragisches Beispiel dafür sind die beiden Flugzeugabstürze der Boing 737 Max, die mehrere Hundert Menschenleben kosteten und durch eine Fehlfunktion der Software der Flugzeugsteuerung verursacht wurden [Tra19,Flo19].

**Digitalisierung von analogen Daten:** Diese Anforderung bestimmt vor allem die Frequenz des eingebetteten Systems, also die Geschwindigkeit, in der es Daten verarbeiten muss, die damit direkt von dem es umgebenden System abhängt.

**Ressourceneffizienz:** Eingebettete Systeme sollen möglichst effizient sein. Das betrifft vor allem folgende Bereiche:

- Energieverbrauch: Viele der Systeme laufen mit Batterien oder Akkumulatoren, die umso länger halten, je energiesparender das System ist.

- Programmgröße: Der Speicher auf eingebetteten Systemen ist üblicherweise stark limitiert, sodass die Anwendung nur begrenzten Platz zur Verfügung hat.

- (Bauteil-)Kosten: Eingebettete Systeme werden oftmals in sehr großen Stückzahlen produziert. Schon kleinste Einsparungen am Hardwareverbrauch kann zu enormen Einsparungen führen.

Da bei eingebetteten Systemen der Zweck bekannt ist (manifestiert durch die bereits vor der Laufzeit bekannte Anwendung), bilden sie eine Unterkategorie der *Spezialzwecksysteme*, die wiederum Systeme sind. In dieser Arbeit sind nur eingebettete Systeme im engeren Sinn relevant.

### 2.1.1 Maßgeschneiderte Systeme durch Optimierung

Alle eben beschriebenen Designziele führen zu der grundlegenden Eigenschaft, dass eingebettete Systeme auf ihre Aufgabe zugeschnitten werden. Konkret bedeutet das, dass weder überflüssige Hardware verbaut wird noch unbenutzte Software installiert ist [Mar21a1.4].

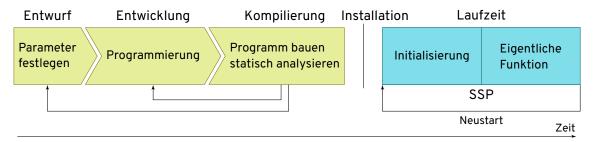

Abbildung 2.2 Verschiedene Lebensphasen von eingebetteten Systemen. Die Phasen vor der Laufzeit sind nicht zwangsläufig streng folgend, sondern können bei Bedarf (wenn eine spätere Phase Probleme aufdeckt) wiederholt werden. Die Laufzeit gliedert sich in Initialisierung und eigentlichem Betrieb, die durch den System Setup Point (SSP) getrennt werden.

Überflüssige Hard- und Software senkt die Zuverlässigkeit. Eine Fehlfunktion eines unnötigen Bauteils oder einer unnötigen Anweisung stellt eine überflüssige Fehlerquelle dar. Unbenutzte Bauteile verbrauchen unnötige Energie und kosten zusätzliches Geld. Überflüssige Funktionen in Software benötigen Prozessorzyklen oder Speicher, der sonst kleiner dimensioniert werden könnte.

Spezialisierung

Die Maßschneiderung wird allerdings mit einem Verlust von Flexibilität erkauft. Das vs. Flexibilität System kann abschließend nur noch für den vorgesehenen Zweck benutzt werden. Um die Software trotzdem aus generischen Bausteinen aufzubauen, läuft die Maßschneiderung (teil)automatisiert ab. Das System wird erst mithilfe von generischen Bausteinen erstellt und getestet und anschließend programmunterstützt optimiert [Gre22].

> Die Systemeigenschaften werden dafür in funktionale und nichtfunktionale Eigenschaften aufgeteilt. Funktionale Eigenschaften sind für das ordnungsgemäße Funktionieren des Systems zwangsläufig zu erfüllen. Nichtfunktionale Eigenschaften haben auf die Korrektheit des Systems keinen Einfluss, eine Verbesserung kann aber aus anderen Gründen wünschenswert sein [Die19A8.3,SWH10A1.1]. Der Energieverbrauch, eine oft nichtfunktionale Eigenschaft, wird z. B. bei Softwareupdates gerne verbessert [Gar22,App22].

> Optimierungen sind Verbesserungen der nichtfunktionalen Eigenschaften des Systems, ohne die funktionalen Eigenschaften zu verändern [DAM08]. Voraussetzung für die Optimierung ist die im letzten Abschnitt beschriebene statische Analyse, die bei eingebetteten Systemen konkret ausnutzen kann, dass die Anwendung dieser Systeme im Vorhinein bekannt und somit eine Analyse des gesamten Systems möglich ist.

### 2.1.2 Lebensphasen

Eine Anwendung für ein eingebettetes System durchläuft verschiedene Phasen. Abbildung 2.2 visualisiert die für diese Arbeit relevanten Phasen schematisch. Begonnen wird

mit der Entwurfsphase, bei der wichtige Systemparameter festgelegt werden. Es folgt die Entwicklungsphase, bei der der konkrete Anwendungscode geschrieben wird. Danach wird das System in der Kompilierphase gebaut, d. h. ein Image für die Zielmaschine erzeugt. Hier ist der Zeitpunkt, zu dem statische Analysen zumeist stattfinden<sup>6</sup>. Alle in dieser Arbeit vorgestellten Analysen finden in dieser Phase statt. Mit dem fertigen Image kann das System ausgerollt ("deployed") bzw. in der Zielmaschine installiert werden. Abschließend kann die Anwendung gestartet werden. Alles in dieser Phase findet zur Laufzeit der Anwendung statt. Innerhalb dieser kann weiterhin der System Setup Point (SSP) definiert werden, System Setup der den Zeitpunkt angibt, an dem das System vollständig initialisiert ist [›FED+21].

Point

### 2.2 Echtzeitsysteme

Echtzeitsysteme (Real-Time Systems, RTSs) sind Systeme, bei der eine Aufgabe nur dann Begriffe: korrekt erfüllt ist, wenn sie zusätzlich in einer vorher festgelegten Frist ("Deadline") er- RTS, RTCS, folgt ist [Liu00A2, Kop11A1.1]. Die Korrektheit des Systems hängt damit von der physi- RTA, RTOS kalischen Größe Zeit ab – der "echten Zeit" –, die somit zu einer funktionalen Eigenschaft wird<sup>7</sup> [Die19A2.1]. In der Literatur wird weiterhin zwischen Echtzeitsystemen und Echtzeitrechensystemen (Real-Time Computing Systems, RTCSs) unterschieden [Die19A2.1]. Letztere beinhalten zwangsläufig einen Computer, während erstere auch rechnerlose, z.B. rein mechanische Maschinen sein können<sup>8</sup>. Ich werde in dieser Arbeit beide Begriffe synonym verwenden und beziehe mich immer auf RTS mit Computer. Auf dem RTCS läuft eine Echtzeitanwendung (Real-Time Application, RTA), die die konkrete Kontrolllogik implementiert, dabei aber für die Aufgabenverwaltung und Synchronisation oft auf ein Echtzeitbetriebssystem (Real-Time Operating System, RTOS) zurückgreift.

RTSs steuern oftmals größere Geräte, in die sie eingebettet sind und zählen folglich zu den eingebetteten Systemen [Kop11A1.6.1]. Abbildung 2.3 erweitert Abbildung 2.1 um den internen Aufbau eines RTSs. Die Sensordaten werden hierbei in der Echtzeitanwendung verarbeitet, was in einem neuen Satz an Aktordaten resultiert.

<sup>&</sup>lt;sup>6</sup> Prinzipiell können diese auch schon verschränkt zur Entwicklungsphase stattfinden. Die Analyse basiert dann aber natürlich auf unvollständigem Code.

$<sup>^7\,</sup>$  Die Aufgabe, meistens eine Reaktion auf ein Ereignis, muss dabei keinesfalls schnellstmöglich passieren, was im Multimediabereich oft mit dem Begriff "Echtzeit" verknüpft wird, sondern zwangsläufig innerhalb der Frist.

<sup>&</sup>lt;sup>8</sup> Praktisch sind diese Systeme schwer zu finden. In den allermeisten RTCSs ist die Frist nur ein Hilfsmittel, um negative Folgen auf eine andere physikalische Größe zu vermeiden (z.B. die "rechtzeitige" Abschaltung eines Kernreaktors bei Überhitzung, oder das fristgerechte Öffnen eines Überdruckventils). Rein mechanisch sind diese Systeme oft über einen direkten Rückkopplungsmechnismus realisiert (z.B. ein Bimetall, das den Wasserkocher abschaltet, oder ein Schwimmerventil, das den Wasserzufluss bei passendem Füllstand schließt). Echte "zeitliche" Fristen, die rein mechnisch realisiert sind, finden sich z. B. beim Aktivieren einer Eieruhr oder codiert über die Länge einer Zündschnur für Sprengstoff.

Kapitel 2 - Eingebettete und Echtzeitsysteme

Abbildung 2.3 Ein Echtzeitsystem. Innerhalb des Systems befindet sich ein Echtzeitrechensystem, das über Sensoren über Aktoren mit der Umgebung verbunden ist. Die Daten werden mithilfe einer Echtzeitanwendung verarbeitet, die wiederum ein Echtzeitbetriebssystem für die Jobkontrolle benutzt (nach [Die19A2.1]).

Eigenschaften Um die Einhaltung der Fristen garantieren zu können, sind Echtzeitsysteme so deterministisch wie möglich angelegt. Insbesondere ist die Prozessplanung üblicherweise prioritätenbasiert und damit zu einem gewissen Grad statisch vorhersagbar. Dadurch kann idealerweise mithilfe einer Echtzeitanalyse nachgewiesen werden, dass alle Fristen unter allen Umständen eingehalten werden. Praktisch verbreitet ist aber oft eine messbasierte Validierung [Liu00A6.1].

> Für Echtzeitsysteme ist die Nomenklatur nicht einheitlich. Ich werde mich in dieser Arbeit konzeptuell hauptsächlich an Liu [Liu00] und Kopetz [Kop11] orientieren und als Nomenklatur die "Burns Standard Notation" [Dav13] verwenden. Eine Übersicht an wichtigen Begriffen findet sich in Tabelle 2.1.

> Im Folgenden stelle ich ausgewählte Konzepte von Echtzeitsystemen und damit auch eingebetteten Systemen vor. Da die Konzepte von allen dort vorherrschenden Betriebssystemen implementiert werden, sind sie essentieller Bestandteil einer betriebssystemgewahren statischen Analyse.

### 2.2.1 Jobs und Tasks

Jobs und Tasks Der Entwurf von Echtzeitsystemen folgt meistens einer strikten Modellierung [Liu00A3]. Die im Vorhinein bekannte Anwendung, die das Echtzeitsystem schlussendlich ausführen soll, lässt sich üblicherweise in Arbeitspakete teilen, sogenannte Tasks. Tasks sind die Entität, die mit einer Frist versehen werden. Sie haben eine Startzeit, wann sie frühestens ausgeführt werden können und sie haben Abhängigkeiten untereinander. Eine konkrete Instanziierung eines Tasks wird Job genannt [Dav13].

Prozessoren Alle Jobs werden auf Prozessoren ausgeführt. Das können "echte" Prozessoren im Sinne von physischen CPU-Kernen sein, das können aber auch Speicher- oder Netzwerkcontroller sein. Sie zeichnen sich dadurch aus, dass sie aktiv einen oder mehrere Jobs ausführen.

| Notation | Terminologie   | Erklärung                                                            |

|----------|----------------|----------------------------------------------------------------------|

| $	au_i$  | Task           | Der Task mit Index i.                                                |

| au       | Tasks          | Menge aller Tasks.                                                   |

| $C_{i}$  | WCET           | Eine obere Grenze der Zeit, die der Task $	au_i$ maximal läuft.      |

| $D_i$    | relative Frist | Die längstmögliche Zeit, die der Task $	au_i$ laufen darf.           |

| $P_{i}$  | Priorität      | Die Priorität des Tasks $	au_i$ .                                    |

| $T_i$    | Periode        | Die minimale Zwischenankunftszeit zwischen Jobs des Tasks $\tau_i$ . |

Tabelle 2.1 Nomenklatur von Echtzeitsystemen (Auswahl, in der "Burns Standard Notation" [Dav13])

Jobs interagieren mithilfe von Ressourcen. Sie stellen Entitäten dar, mit denen Daten aus- Ressourcen getauscht werden können und die in einer festgelegten Menge vorkommen. Beispielsweise lässt sich ein Sensor als Ressource modellieren, die exklusiven Zugriff bietet (sodass Daten nicht gleichzeitig gelesen werden können). Ressourcen können dabei beansprucht und wieder freigegeben werden (semantisch ähnlich zu einem Mutex oder Lock).

Die Modellierung in Jobs/Tasks, Prozessoren und Ressourcen ist entwicklerabhängig. Beispielsweise kann ein Speicher als Prozessor modelliert werden (der mit einer gewissen Latenz aktiv Daten bereitstellt oder wegschreibt) als auch als Ressource (die exklusiv angefordert werden kann).

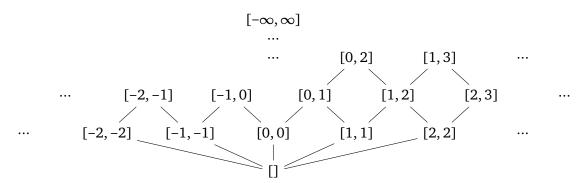

Eine wichtige Größe beim Systementwurf ist die schlechtmöglichste Ausführungszeit (Worst- WCET Case Execution Time, WCET), die eine obere Grenze der Ausführungsdauer eines Task vorgibt. Die Bestimmung der WCET ist dabei nicht trivial und Gegenstand aktueller Forschung [Mar21A5.2]. Probleme hierbei sind vor allem fehlende Hardwaremodelle ("Wie lange braucht die Hardware für diesen Befehl?") [AGV+22] und ein nicht trivialer Kontrollfluss der Anwendung (z. B. verhindern Programmschleifen ohne obere Grenze ihrer Durchläufe jegliche WCET-Analyse). Der WCET steht die bestmöglichste Ausführungszeit (Best-Case Execution Time, BCET) gegenüber, die eine untere Grenze der Ausführungszeit angibt. Die nicht verbrauchte Zeit zwischen BCET und WCET heißt Schlupf ("slack").

### 2.2.2 Fristen ("Deadlines")

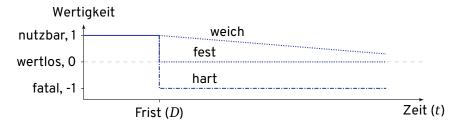

Bei Fristen wird oft zwischen harten, festen und weichen Fristen unterschieden [Liu00A2, Kop11a1.5,SR94] (Abbildung 2.4). Harte Fristen sind Fristen, deren Überschreiten fatale Folgen hätte. Der Wert des Ergebnisses ist in diesem Fall negativ. Beispielsweise kann das nicht rechtzeitige Reagieren eines Hilfssystems im Automobil (wie eines Airbags) tödliche Folgen haben. Bei weichen Fristen hingegen ist ein Überschreiten nicht wünschenswert, aber

**Abbildung 2.4** Weiche, feste und harte Fristen. Das Ergebnis einer Berechnung hat je nach Typ eine andere Wertigkeit. Die abfallende Wertigkeit bei weichen Fristen ist hier nur beispielhaft eine lineare Funktion.

verkraftbar: Der Wert des Ergebnisses ist reduziert, aber noch vorhanden. Eine Verzögerung bei der Dekodierung von Videobildern z.B. führt zu einem Ruckeln des Videos oder zur Artefaktbildung, die zwar unschön sind, aber keinen Personenschaden anrichten. Wird eine feste Frist überschritten, treten keine fatalen Folgen ein, aber das Ergebnis verliert unmittelbar jeglichen Wert. Beispielsweise stellt das rechtzeitige Erreichen eines Zuges eine feste Frist dar: Wird der Zug verpasst, ist das Ziel unabhängig von der Dauer der Verspätung nicht erreicht.

Obige Definitionen ziehen die Frage nach sich, wie genau der Wert bemessen wird. Dieser muss situationsbezogen entschieden werden und ist stark abhängig vom Systemdesigner. Liu [Liu00A2.3.2] zieht z. B. die Grenze zwischen harten und weichen Fristen aus diesem Grund wie folgt: Wann immer ein Benutzer vom Entwickler verlangt, die Einhaltung einer Frist zu validieren oder zu verifizieren, handelt es sich um eine harte Frist (im Vergleich zur weichen Frist).

### 2.2.3 Ablauf planung ("Scheduling")

Kernaufgabe eines Echtzeitsystems ist die korrekte Einhaltung der Fristen, die von mehreren Jobs mit unterschiedlichen Ausführungszeiten und Abhängigkeiten untereinander vorgegeben werden. Ein Problem entsteht dabei dadurch, dass Jobs auf Prozessoren ausgeführt werden müssen und üblicherweise weniger Prozessoren als Jobs existieren. Normalerweise wird der Prozessor dazu über die Zeit gemultiplext, d. h. verschiedenen Jobs exklusiv zugeteilt. Im einfachsten Fall ist dies eine bloße Hintereinanderausführung. Soll nun ein Job mit einer langen Frist, aber kurzen Laufzeit starten, kann bei guter Planung problemlos ein weiterer kurz laufender Job "zwischengeschoben" werden, ohne Fristen zu verletzen. Diese Art Planung wird vom Ablaufplaner (Scheduler) erledigt. Können Jobs unterbrochen und verdrängt werden, heißt dies präemptive Ablaufplanung<sup>9</sup>. Die eigentliche Prozessorzuteilung

<sup>&</sup>lt;sup>9</sup> Präemption wurde bereits 1962 verwendet, um *Timesharing* zu implementieren, bei dem Jobs periodisch den Prozessor erhalten, um gleichzeitige Ausführung zu simulieren [CMD62].

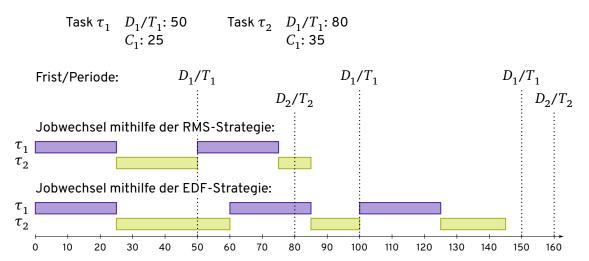

Abbildung 2.5 Ein Set an Tasks, das einmal mit der RMS-Strategie und einmal mit der EDT-Strategie geplant wird. RMS findet in diesem Fall im Gegensatz zu EDF keine gültige Strategie. Die Auslastung des Systems ist mit  $\frac{25}{50} + \frac{35}{80} = 0.94$  über den etwa 69%, die RMS fehlerlos planen kann (Beispiel nach [SGG05A19.5])

läuft prioritätenbasiert [SGG05A19.4]. Für die technische Umsetzung sind zwei Komponenten zuständig: Der Ablaufplaner trifft nach einer Scheduling-Strategie die Entscheidung, welcher Job laufen soll. Die eigentliche Durchsetzung der Entscheidung übernimmt der Dispatcher [Die19A2.1.2].

RTSs unterscheiden sich hier in zwei grundlegende Konzepte: Ereignisgetriebene (event-dri- ereignisven) und zeitgetriebene (time-driven) RTS [Liu00A4.4,Kop11A1.5.5]. Erstere reagieren getriebene und dynamisch auf Ereignisse (die für gewöhnlich über Interrupts signalisiert werden). Letztere zeitgetriebene arbeiten nach einem festen Zeitplan periodisch alle Ereignisse ab. Zeitgetriebene Systeme RTS haben den Vorteil, dass sämtliches Scheduling offline, d. h. vor der Laufzeit erledigt werden kann. Ereignisgetriebene Systeme sind dafür insbesondere bei Ereignissen, die in unterschiedlicher Frequenz auftreten, ressourceneffizienter, da sie keine feste Periode setzen müssen, die entweder die schnellen Frequenzen nicht abdeckt oder sehr klein ist, aber dafür oft überflüssige Systemlast erzeugt. In dieser Arbeit werden wir uns ausschließlich mit ereignisgetriebenen Echtzeitsystemen beschäftigen.

Die Ablauf planung teilt die (begrenzte) Ressource "Prozessorzeit" verschiedenen konkurrierenden Jobs zu. Es dient aber überdies zur Abhängigkeitsmodellierung der Jobs untereinander. Hängt ein Job von einem anderen ab, kann dies im System so modelliert werden, dass der letztere den ersten (mithilfe des Planers) aktiviert und damit lauffähig macht. Diese Abhängigkeiten sind bei ereignisgetriebenen Systemen explizit durch Systemaufrufe, bei zeitgetriebenen Systemen aber nur implizit modelliert, da sie im vorher berechneten Plan "einfach" hintereinander eingeplant werden (ein wesentlicher Mechanismus in der Analyse des RTSC, siehe Abschnitt 4.4).

Bei ereignisgetriebener Planung gibt es mehrere Strategien, von denen *Rate Monotonic Scheduling (RMS)* und *Earliest Deadline First (EDF)* am populärsten sind [SGG05A19.5]. Beide arbeiten prioritätenbasiert. Jedem Task wird dafür eine solche zugeordnet. Die Ablaufplanung folgt dann der Regel, dass der lauffähige Task mit der höchsten Priorität den Prozessor erhält.

RMS arbeitet nach dem Prinzip, dass die Prioritätenzuordnung statisch erfolgt: Je kürzer die Periode des Tasks ist, desto höher ist die Priorität. Dieses Scheduling-Verfahren ist einfach (und effizient) zu implementieren, aber nicht optimal. Es garantiert nicht, dass ein Ausführungsplan gefunden wird, wenn einer existiert. Konkret garantiert RMS, dass ein möglicher Ausführungsplan gefunden wird, wenn die Systemauslastung unter  $\ln 2$  (etwa 70%) liegt [Liu00A6.7].

EDF ordnet die Prioritäten dynamisch zu: Der Task mit der kürzesten relativen Deadline bekommt die momentan höchste Priorität. Dieses Verfahren ist unter der Voraussetzung, dass jeder Task unterbrechbar ist, und ausschließlich für Einkernsysteme optimal<sup>10</sup> [Liu00A4.6]. Wird EDF auf einem System implementiert, das initial mit statischen Prioritäten geplant hat, müssen bei jedem Kontextwechsel die Prioritäten neu berechnet werden. EDF braucht außerdem einen Zähler für absolute Zeit (auf unter 32-Bit-Systemen praktisch kompliziert) und trifft keine vorhersagbare Aussage darüber, was bei Überlastsituationen passiert, da im Gegensatz zu RMS nicht immer derselbe Task bevorzugt wird [But05,BG06]. Aus diesen Gründen wird in der Praxis oft RMS bevorzugt. In Abbildung 2.5 werden beispielhaft die Ergebnisse beider Algorithmen auf einem Set an Tasks dargestellt. RMS findet in diesem Beispiel im Gegensatz zu EDF keinen funktionierenden Ablaufplan.

In dieser Arbeit spielt die Scheduling-Strategie technisch eine Rolle, da sie vom Betriebssystemmodell interpretiert werden muss. Gerade Scheduling-Algorithmen für Echtzeitsysteme erleichtern aber die statische Analyse derselben, da sie wohldefiniert und deterministisch sind und daher die Scheduling-Entscheidung oftmals vorausberechnet werden kann.

### 2.3 Echtzeitbetriebssysteme

Echtzeitbetriebssysteme (Real-Time Operating Systems, RTOSs) sind Programme, die unterstützenden Code für die eben beschriebenen Konzepte implementieren. Der Scheduler und der zugehörige Kontextwechselmechanismus sind z.B. Kernkomponenten eines RTOSs [SGG05A19.4]. Die betriebssystemgewahren Analysen in dieser Arbeit setzen genau an der Schnittstelle zwischen Anwendung und RTOS an, den Systemaufrufen, und operieren auf einem Betriebssystemmodell, das die Betriebssystemkonzepte abstrakt repräsentiert.

$<sup>^{10}</sup>$  Dies gilt genaugenommen nur in der Theorie, da auch der Kontextwechsel selbst Zeit in Anspruch nimmt [SGG05 $_{\rm A}$ 19.5.2].

Das zentralste Konzept eines RTOSs ist das der Aktivität: Diese beschreibt zusammenhän- Aktivitäten: gende Code-Teile, die vom RTOS bzw. der Hardware selbst zeitlich auf dem Prozessor Fäden und ISRs multiplext werden und untergliedert sich in Fäden (Threads) und Interrupt Service Routines (ISRs) [Die19A2.1.2]. Multiplexing von beschränkten Ressourcen, von denen der Prozessor die wichtigste darstellt, ist eine der Hauptaufgaben von Betriebssystemen. Um den Prozessor zeitlich zu multiplexen, verwendet es Fäden, die sich gegenseitig abhängig von der Scheduling-Strategie unterbrechen können. Diese sind für die ausgeführte Applikation gleichbedeutend mit einem virtuellen Prozessor, insbesondere ist es für einen Faden nicht ohne weiteres feststellbar, dass er unterbrochen wurde. Aus diesem Grund müssen Betriebssysteme bei Fäden (äquivalent zu einem echten Prozessor) einen Program-Counter mitführen und in den meisten Fällen auch noch zusätzliche Register, die zum Kontext des Prozessors gehören<sup>11</sup>. In RTOSs werden Jobs in vielen Fällen auf Fäden abgebildet [Liu00A12.1]. Es ist aber auch möglich, mehrere Jobs innerhalb eines Fadens auszuführen. Konkret werde ich darauf in Abschnitt 2.4 eingehen.

Neben Fäden kann der Prozessor auch noch ISRs ausführen. Im Gegensatz zu Fäden, die durch Software ausgelöst werden, werden ISRs durch die Hardware, konkret durch eine Unterbrechung (Interrupt), ausgelöst, können Fäden unterbrechen, werden aber (für gewöhnlich) nicht von diesen unterbrochen. Liegt eine Unterbrechung an (Interrupt Request (IRQ)), springt der Prozessor zu einer Interrupt-spezifischen Behandlungsroutine. In den im Folgenden vorgestellten RTOSs sind ISRs zusätzlich zu Fäden explizit modelliert, in der Literatur wurde aber gezeigt, dass Fäden bzw. sämtliche Kontrollflüsse als ISRs modelliert werden können [Hof14,RSK03] und daher auch hier nach Dietrich gemeinsam unter dem Begriff "Aktiviät" fungieren [Die19A2.1.2].

RTOSs definieren außerhalb von Aktivitäten zumeist noch weitere Konzepte. Üblicherwei- Instanzen se sind das Konzepte zur Synchronisation zwischen Fäden (z. B. Semaphoren, Mutexe, Ressourcen), der Signalisierung (z. B. Events) oder der Kommunikation inkl. Nutzdaten (z. B. Messagequeues, Queues). Manche Systeme definieren weiterhin Abstraktionen für die Hardware oder Netzwerke (z. B. Sockets). Für die später in dieser Arbeit beschriebenen Analysen ist in diesem Zusammenhang der Begriff der Instanz (eines virtuellen Betriebsmittels) von entscheidender Bedeutung. Ich will ihn daher hier definieren:

#### Definition 2: (Betriebsmittel-)Instanz.

Eine Instanz ist eine konkrete Ausprägung eines (virtuellen) Betriebsmittels im laufenden System. Virtuelle Betriebsmittel wiederum sind Abstraktionen des Betriebssystems, die den vorgesehenen Betrieb ermöglichen<sup>12</sup>. Der Begriff "Betriebssystemobjekt" wird oft synonym mit einer Instanz verwendet.

$<sup>^{11}</sup>$  Auch in dem RTOS-Modell, das ich für diese Arbeit verwende, finden diese Felder Verwendung

$<sup>^{12}</sup>$  Genaugenommen ist der Begriff "Instanz" eine Fehlübersetzung des englischen "instance", die sich aber in der Informatik etabliert hat und die ich daher hier übernehme. Besser wäre "Exemplar".

Beispiele für Instanzen sind Instanziierungen von virtuellen Betriebsmitteln wie Fäden, Semaphoren, Messagequeues usw., also z. B. der konkrete "Motor-Control-Thread" oder der "Modem-Mutex". Instanzen sind damit die zentralen Bausteine einer RTOS-Schnittstelle, da sie die Objekte darstellen, mit denen die Anwendung moderiert über das RTOS Betriebsmittel benutzen kann.

Über die Zeit sind viele RTOS-Implementierungen entstanden. Diese Arbeit wird sich vor allem auf vier Implementierungen konzentrieren, die so gewählt sind, dass sie zusammen ein breites Spektrum an Konzepten abdecken. Vor allem fällt die verschiedenartige Instanziierung auf. Die Instanzen können dabei entweder statisch in der Kompilierphase, oder dynamisch, d. h. zur Laufzeit, angelegt werden. Tabelle 2.2 fasst die konzeptuellen Unterschiede zusammen. Eine Tabelle konkreter Systemaufrufe findet sich in Anhang A.1. Ich werde die einzelnen RTOSs im Folgenden kurz vorstellen.

| Konzept                                | AUTOSAR   | FreeRTOS                             | Zephyr                                                 | POSIX                        |

|----------------------------------------|-----------|--------------------------------------|--------------------------------------------------------|------------------------------|

| Art                                    | Standard  | Implementierung                      | Implementierung                                        | Standard                     |

| Einsatzzweck                           | RTS       | RTS/<br>Eingebettete Systeme         | RTS/<br>Eingebettete Systeme                           | Universell                   |

| Instanziierung                         | Statisch  | Dynamisch                            | Statisch/Dynamisch                                     | Dynamisch                    |

| Konfiguration                          | DSL (OIL) | C-Makros                             | DSL (KConfig)                                          | kA                           |

| Scheduler                              | RMS       | RMS                                  | konfigurierbar                                         | konfigurierbar               |

| Virtuelle<br>Betriebsmittel<br>(u. a.) |           | Tasks<br>Semaphoren<br>Notifications | Threads<br>Semaphoren<br>Mutexe<br>Bedingungsvariablen | Threads<br>Mutexe<br>Signale |

**Tabelle 2.2** Konzeptueller Vergleich der verschiedenen RTOSs. Die Art beschreibt, ob es sich um einen Standard (ggf. mit mehreren Implementierungen) oder eine Implementierung (ohne Standard) handelt. Einige RTOSs werden über eine domänenspezifische Sprache (Domain Specific Language, DSL) konfiguriert.

### **2.3.1 AUTOSAR**

AUTOSAR (AUTomotive Open System ARchitecture) ist ein Zusammenschluss großer Automobilhersteller oder -zulieferer, mit dem Ziel, eine gemeinsame Softwareplattform für den Einsatz in Automobilen zu schaffen. Er wurde 2002 gegründet [AUT24].

Ein Bestandteil der Gesamtplattform ist die "AUTOSAR Classic Platform", die Standards für "Embedded Control Units" definiert. Innerhalb dieser Standards ist für diese Arbeit AUTOSAR OS relevant, das einen Standard für ein RTOS darstellt [AUT20]. AUTOSAR

OS basiert auf dem älteren OSEK-OS<sup>13</sup> [OSE05], erweitert dieses aber hauptsächlich um Mehrkernunterstützung. Wenn ich in dieser Arbeit von AUTOSAR spreche, dann meine ich damit immer den Betriebssystemstandard.

Mehrkernunterstützung in AUTOSAR ist über einen partitionierten Scheduler umgesetzt: Der Scheduling-Algorithmus läuft auf jedem Kern separat. Die meisten Instanzen müssen dazu fest einem Kern zugeordnet werden (in AUTOSAR heißen diese dann "Locatable Entities"). Insbesondere sind Tasks fest einem Kern zugeordnet und wechseln niemals. Systemaufrufe betreffen im Standardfall nur den eigenen Kern. Einige Systemaufrufe haben einen fest definierten Effekt auf einen oder mehrere spezifizierte andere Kerne.

AUTOSAR arbeitet ausschließlich mit statischer Instanziierung. Instanzen müssen bereits Instanziierung in der Entwicklungsphase definiert werden, sodass die Instanziierung in der Kompilier- und Konfiguration phase geschieht. AUTOSAR definiert hierfür eine domänenspezifische Sprache (Domain Specific Language, DSL), die OSEK Implementation Language (OIL), in der alle wichtigen Instanzparameter festgelegt werden können. Der Standard hat ein natives Verständnis von Tasks, die der Scheduler direkt verwaltet. Tasks können sich gegenseitig aktivieren oder verketten. Dies ist auch über Kerngrenzen hinweg möglich<sup>14</sup>.

AUTOSAR plant auf fest zugewiesenen Prioritäten. Um Prioritätsinversion in kritischen PCP Bereichen und Deadlocks zu vermeiden, implementiert es dabei das Priority Ceiling Protocol (PCP), das Tasks, die einen kritischen Bereich betreten, temporär eine ggf. höhere dynamische Priorität zuordnet [Liu00A8.6,AUT20]. Dieser entspricht der höchsten Priorität aller Tasks, die potentiell im kritischen Bereich konkurrieren ("ceiling priority"). Der Standard spezifiziert dazu Ressourcen, die ein Task zu Beginn eines kritischen Bereichs anfordert und anschließend wieder freigibt. Die Berechnung der passenden Priorität kann dabei nur statisch erfolgen, somit ist auch die Ressourcenzuordnung zu Tasks zwingend statisch. Ressourcen synchronisieren ausschließlich Tasks auf dem gleichen Kern.

Für die Synchronisation zwischen Kernen definiert AUTOSAR Spinlocks. Diese sind aller- Mehrkern: dings nicht Deadlock-frei und Tasks können verhungern. Der Standard empfiehlt daher, Sperren Sperren nicht zu verschachteln. Prinzipiell wurde bereits 1990 eine Erweiterung des PCP für mehrere Kerne entworfen [Raj90]. Dieser Mechanismus ist allerdings nicht durch den Standard berücksichtigt [LBR11]. Weiterhin haben Wieder und Brandenburg eine umfassende Analyse verschiedener Locktypen in AUTOSAR vorgenommen, in der sie zu dem

Schluss kommen, dass der Locking-Mechanismus, so wie er aktuell ist, die Planbarkeit

$<sup>^{13}\,</sup>$  OSEK steht kurz für "Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug" und war ein Vorgängerkonsortium aus Automobilunternehmen.

<sup>&</sup>lt;sup>14</sup> AUTOSAR unterscheidet hier weiterhin zwischen "Basic Tasks" und "Extended Tasks", wobei erstere nicht warten dürfen und somit von einer höherprioren Aktivität unterbrochen werden können. Der technische Vorteil davon ist, dass sich alle Basic Tasks einen Stack teilen können. Für die Analysen in dieser Arbeit spielt die Unterscheidung allerdings keine Rolle.

deutlich verringert und eine feinere Spezifikation, insbesondere mit geordneten Spinlocks, sinnvoll wäre [WB13].

Zur Signalisierung definiert AUTOSAR weiterhin *Events*. Tasks können auf Events warten oder auch welche senden. Diese werden in einer Maske gespeichert und sind über Kerngrenzen hinweg verfügbar.

### 2.3.2 **POSIX**

POSIX (Portable Operating System Interface) ist eine Familie von Standards [Var22]. Diese wurde zuerst als Versuchsversion 1986 veröffentlicht [Isa90], hat seitdem mehrere Neuauflagen erhalten, zuletzt 2018, und wird von der Austin-Group entwickelt [ISO18].

Der Sinn von POSIX ist es, Schnittstellen zu definieren, die benutzt werden können, um portable Anwendungen zu schaffen. Der Standard definiert dazu eine Schnittstelle zum Betriebssystem (auf Basis von UNIX) inkl. Hilfsfunktionen der C-Standardbibliothek, eine Shell-Laufzeitumgebung und Hilfsprogramme.

Für die Systemschnittstelle sind etwa 1200 Funktionen definiert, die Konzepte wie Threads, Dateien und Pipes, Signale und Sockets festlegen. Sie beinhaltet aber auch Funktionen wie strcpy(), also eine Klasse an Hilfsfunktionen für gängige Programmierprobleme. POSIX beinhaltet zudem eine Echtzeit-Erweiterung, die striktere Vorgaben an Scheduling und Speicherverwaltung stellt. Die POSIX-Systemschnittstelle wird von der libc implementiert, die dann wiederum für einige Funktionen auf Systemaufrufe zurückgreift, die Teil der jeweiligen Betriebssystemschnittstelle sind [The23,Fre23].

In dieser Arbeit beschäftige ich mich ebenfalls mit POSIX, werde dort aber nur ein Subset beachten, der für eingebettete Systeme eine Rolle spielt, insbesondere werde ich ausschließlich Systemaufrufe nach Definition 4 beachten.

Im Gegensatz zu AUTOSAR als Beispiel für eine Schnittstelle mit statischen Instanzen und sehr genauer Spezifikation aller Mechanismen ist POSIX ein Beispiel für eine Schnittstelle, die ausschließlich dynamische Instanzen beinhaltet und auch sonst versucht, ein Maximum an Einsatzzwecken zu erfüllen, dadurch aber oftmals unspezifischer ist oder mehrere Möglichkeiten anbietet.

### 2.3.3 FreeRTOS

FreeRTOS ist ein Open-Source-RTOS, dessen Entwicklung 2003 gestartet wurde und inzwischen maßgeblich von Amazon vorangetrieben und betreut wird [Ric20,Git22].

Es ist wie POSIX ein vollständig dynamisches System, stellt aber insgesamt (vergleichbar mit AUTOSAR) weniger Funktionen zur Verfügung. Sämtliche Instanzen müssen zur

Laufzeit erstellt werden<sup>15</sup>. *Tasks* bei FreeRTOS sind als Fäden im klassischen Sinne implementiert [Ama23]. Insbesondere werden sie zu einem beliebigen Zeitpunkt erstellt, dabei automatisch lauffähig und dann einmalig gestartet. Um dennoch periodisch arbeiten zu können, implementieren sie oftmals eine Endlosschleife.

Andere Betriebssystemobjekte in FreeRTOS sind *Queues* zum synchronisierten, gepufferten Austausch von Daten und *Semaphoren*, *Mutexe* und *Streambuffer*, die synchronisierten ungepufferten Datenaustausch zwischen Threads ermöglichen. Semaphoren und Mutexe sind bei FreeRTOS intern vollständig auf die bereits synchronisierte Queue-Implementierung abgebildet.