Data-Flow Analysis for Fault-Equivalence Set Forming on the ISA Layer

- Typ der Arbeit: Bachelorarbeit

- Status der Arbeit: abgeschlossen

- Projekte: CLASSY-FI

- Betreuer: Oskar Pusz, Christian Dietrich, Daniel Lohmann

- Bearbeiter: Zena Obeidi

- Ende der Arbeit: 01. Mar 2019

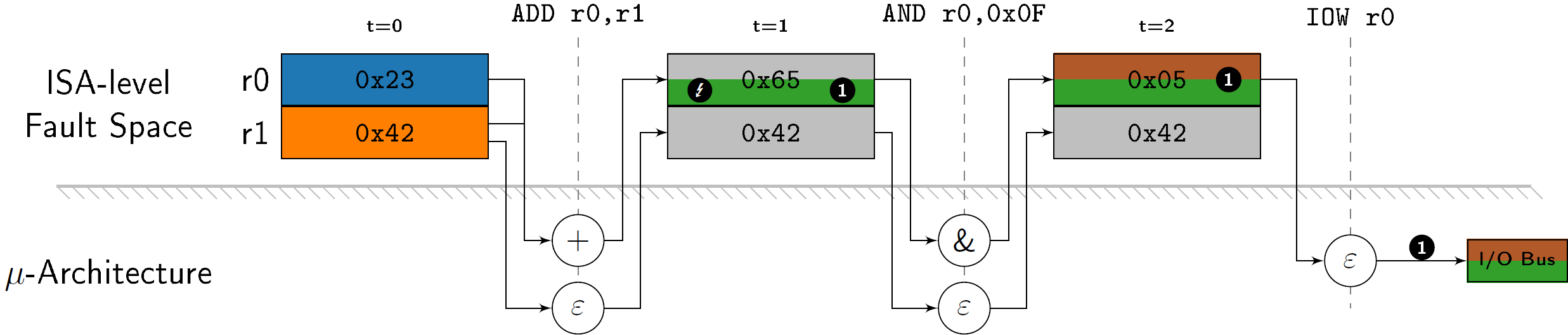

Testing fault tolerance mechanisms is commonly done by performing extensive fault injection experiments on a system that try to mimic physical causes of radiation effects like soft errors/bit flips and then observing the system’s behaviour. There are many possibilities for such injections: Every bit in every cycle. This spans a so-called fault space and one of the first steps is determining equivalent sets of possible injection points which lead to the same system's behaviour to reduce the number of injections needed to test the functional reliability of the system. A common technique is the so-called def/use pruning.

The Instruction Set Architecture (ISA) is an abstract model of a computer and defines in general supported data types, machine state (incl. memory and registers), the instructions set and a model for input and output. This layer is one of the higher and more abstract layers and generalise possible fault injections due to a fault spaces of lower layers. The focus of the thesis is on analysing the ISA layer and the micro-architecture layer is handled as a black box for micro operations.

One task of this thesis is to develop a tool to extract the data flow of an application on ISA layer and one other task is to extend this tool with an analysis of the data flow and determine fault equivalence sets (see the picture above). The goal is to get less rigid equivalence sets in comparison to the def/use pruning based on a concrete data flow or rather a program trace.