Formalizing the Execution Semantics of the AVR Instruction Set with the Description Language SAIL

- Typ der Arbeit: Bachelorarbeit

- Status der Arbeit: abgeschlossen

- Projekte: CLASSY-FI

- Betreuer: Christian Dietrich, Oskar Pusz, Daniel Lohmann

- Bearbeiter: Luca Nedaskovskij

- Ende der Arbeit: 16. Oct 2020

Fault injection mimics either physical causes for single event upsets (by exposing the system to e.g. heat or radiation) or their effects (by changing logic signals). For the fault injection, we use the simulation-based fault injection framework FAIL*, which extracts program traces and simulates the representative faults.

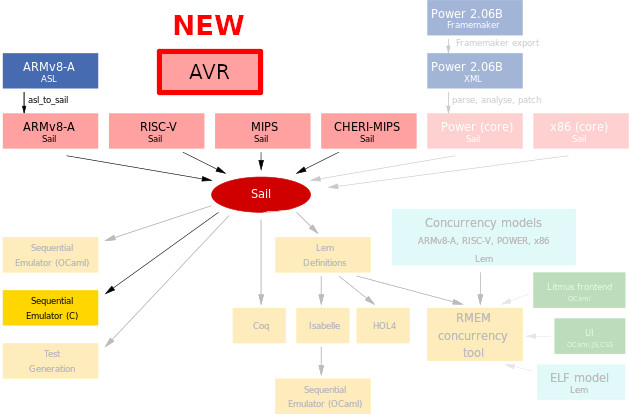

SAIL is a imperative language for describing the instruction-set architecture (ISA) semantics of processors. Given a Sail definition, the tool can generate executable emulators in C language. So, one can use definitions of different ISAs on the basis of one single tool including type and sanity checking.

The main goal of this thesis is to implement an specific AVR-ISA definition written in SAIL. The corresponding generator inside the fault-injection framework FAIL* should generate an emulator automatically.

The next step will be evaluating the integrated architecture comparing to other existing architectures regarding to their resilience against such faults using the simulation-based fault injection framework FAIL*.

Recommended Skills and Interests🔗

- Will to learn SAIL

- Experiences in C/C++ and its tooling

- Interest in implementing an instruction set